适用于DRAM和处理器的3D堆栈集成

东京科学研究所在 IEEE电子元件和技术会议 ECTC 上透露了其 BBCube 3D 集成流程的进展。

本文引用地址:https://www.eepw.com.cn/article/202506/471581.htm

“这些新技术可以帮助满足高性能计算应用的需求,这些应用需要高内存带宽和低功耗以及降低电源噪声,”该研究所表示。

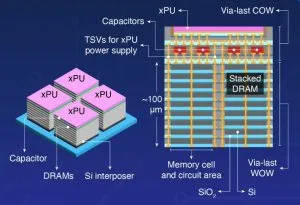

BBCube 结合使用晶圆上晶圆 (WOW) 和晶圆上芯片 (COW) 技术,将处理器堆叠在一堆超薄 DRAM 芯片上。

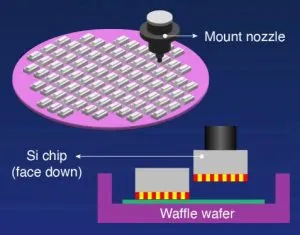

将处理器放在顶部有助于散热,而该研究所的面朝下的 COW 工艺最初是为了摆脱焊接互连而开发的,而是在室温下使用喷墨选择性粘合剂沉积。

用于 300mm 晶圆,实现了 10μm 的芯片间距和 <10ms 的安装时间。

“在Wafer晶圆上制造了 30,000 多个不同大小的芯片,没有出现任何芯片脱落故障,”项目研究员 Norio Chujo 说。

第一篇 ECTC BBCube 改进论文涵盖了一种名为 DPAS300 的定制粘合剂,该粘合剂针对超薄晶圆的 COW 堆栈中的热稳定性进行了优化。

“通过仔细设计化学特性,[这种] 新型胶粘剂材料可用于 COW 和 WOW 工艺,”该研究所说。“它由有机-无机杂化结构组成,在实验研究中] 表现出明显的粘合性和耐热性。”

第二篇论文描述了改进的配电,在 DRAM 堆栈和顶部处理器之间添加了嵌入式去耦电容器,在华夫格晶圆上实施了再分配层,并在晶圆通道和 DRAM 划线中添加了硅通孔(见图)。

“这”将数据传输所需的能量降低到传统系统的五分之一到二十分之一,同时还将电源噪声抑制到 50mV 以下,“Chujo 说。

评论