- 多年来,处理器在专注于性能的同时几乎没有对其他任何东西负责。但现在,性能虽然还是很重要的参考指标,但处理器还必须对功耗负责。

- 关键字:

处理器 架构 处理器优化 功耗

- 德国RISC-V 处理器开发商Codasip的董事会将要出售公司。该公司在首席执行官 Ron Black 的领导下,希望在未来三个月内出售该公司。它开发了使用开放式 RISC-V 指令集生产处理器内核的工具,并获得了高达 380m 欧元的资金,其中包括各种股权和赠款,其中包括后续项目资金。目前有 250 名员工,其中 57% 从事硬件工作,30% 从事软件工作。近年来,RISC-V 开发一直在努力,市场竞争更加激烈。Synopsys 去年推出了全系列 RISC-V 内核 IP,而主要芯片制造商的

- 关键字:

RISC-V 处理器 Codasip

- 东京科学研究所在 IEEE电子元件和技术会议 ECTC 上透露了其 BBCube 3D 集成流程的进展。“这些新技术可以帮助满足高性能计算应用的需求,这些应用需要高内存带宽和低功耗以及降低电源噪声,”该研究所表示。BBCube 结合使用晶圆上晶圆 (WOW) 和晶圆上芯片 (COW) 技术,将处理器堆叠在一堆超薄 DRAM 芯片上。将处理器放在顶部有助于散热,而该研究所的面朝下的 COW 工艺最初是为了摆脱焊接互连而开发的,而是在室温下使用喷墨选择性粘合剂沉积。用于 300mm 晶圆,实现了 10μm 的

- 关键字:

DRAM 处理器 3D堆栈集成

- 一块搭载了英伟达N1X处理器的惠普开发板(HP 83A3)在Geekbench上亮相。在Geekbench的测试中,运行Linux(Ubuntu 24.04.1)的N1X处理器在单核测试中获得了3096分,在多核测试中获得了18837分,平均频率为4GHz。数据显示这款处理器为20线程配置,由于Arm通常没有像英特尔那样的超线程技术,因此很可能是20个物理核心,类似于英伟达迷你超算所搭载的GB10。同时,该开发板可能配备128GB系统内存,其中8GB预留给GPU。其性能已经接近甚至超过了当前市场上的一些顶

- 关键字:

英伟达 Arm PC 芯片 SoC 处理器 联发科

- 全新英特尔至强6处理器:为满足AI模型和数据集增长需求而生;英特尔至强6家族又添新成员:释放GPU潜能,AI性能更出色

- 关键字:

英特尔 至强6 处理器 GPU AI性能

- 5 月 27 日消息,小米创办人、董事长兼 CEO 雷军今日早发文:“玄戒 O1 最高主频 3.9GHz,这足以说明我们芯片团队已经具备相当强的研发设计实力。”官方数据显示,小米玄戒

O1 处理器安兔兔跑分超过了 300 万分,拥有 190 亿个晶体管,采用了全球最先进的 3nm 工艺,芯片面积仅

109mm2。架构方面,小米玄戒 O1 采用了十核四丛集 CPU,拥有双超大核、4 颗性能大核、2 颗能效大核、2 颗超级能效核,超大核最高主频

3.9Hz,单核跑分超 3000 分,多核跑分超 9

- 关键字:

小米 雷军 芯片 玄戒 O1 处理器 ARM 3nm

- 5月20日消息,高通周一宣布,将推出数据中心专用AI处理器,可实现与英伟达芯片的互联互通。英伟达GPU已成为训练大语言模型的关键硬件,通常需与CPU搭配使用——后者被英特尔/AMD双雄垄断。高通计划推出定制化数据中心CPU,该产品不仅兼容英伟达GPU及软件栈,更深度整合CUDA生态。在英伟达占据AI算力霸主地位的当下,实现与英伟达技术生态的深度整合,是破局数据中心市场的关键。这标志着高通二度进军数据中心市场——此前十年间多次尝试均告失利。2021年收购专注Arm架构处理器设计的Nuvia,为其数据中心战略

- 关键字:

高通 CPU 英伟达 英特尔 AMD AI 处理器

- 5 月 10 日消息,科技媒体 notebookcheck 昨日(5 月 9 日)发布博文,报道称英伟达首款

ARM 架构的“超级芯片”GB10 Grace Blackwell 现身 GeekBench 跑分库,性能数据虽有波动,但单核性能已能与高端

ARM 和 x86 处理器一较高下。该媒体认为从现身 GeekBench 数据库来看,这款芯片已进入测试阶段,英伟达有望在 2025 台北国际电脑展(5 月 20~23 日)上正式发布该芯片。GB10 的单核性能表现亮眼,跑分数据表明其能与顶级 AR

- 关键字:

英伟达 ARM 超级芯片 处理器

- 恩智浦半导体今天推出采用 16 纳米 FinFET 技术的新型 S32R47 成像雷达处理器,该处理器以恩智浦在成像雷达领域的成熟专业知识为基础。S32R47 系列是 NXP 性能最高的雷达处理器,可满足 2+ 至 4 级自动驾驶的苛刻要求更高分辨率的传感支持高级用例,例如检测易受攻击的道路使用者 (VRU) 和丢失的货物更强大的计算能力使 OEM 能够开发高级应用程序,例如自动驾驶仪导航,同时大规模满足未来软件定义汽车 (SDV) 的需求荷兰埃因霍温,2025 年 5 月 8 日 (GLOBE NEWS

- 关键字:

恩智浦 自动驾驶 成像雷达 处理器

- 4 月 14 日消息,英特尔核心设计团队高级首席工程师 Ori Lempel 在接受外媒 KitGuru 采访上表示,该企业在酷睿 Ultra 2000 系列客户端处理器中取消性能核(P Core)的超线程,与无超线程设计更优秀的同功耗面积下表现密切相关。Ori

Lempel 表示,根据经验估算数据,相较硬件上支持超线程 / 同步多线程 (SMT) 但关闭这一功能的核心,开启超线程能提升 30% 的

IPC 但会增加 20% 的功耗,而硬件设计上不支持超线程的核心能在相同 IPC 下降低 15%

- 关键字:

英特尔 客户端 处理器 超线程 功耗

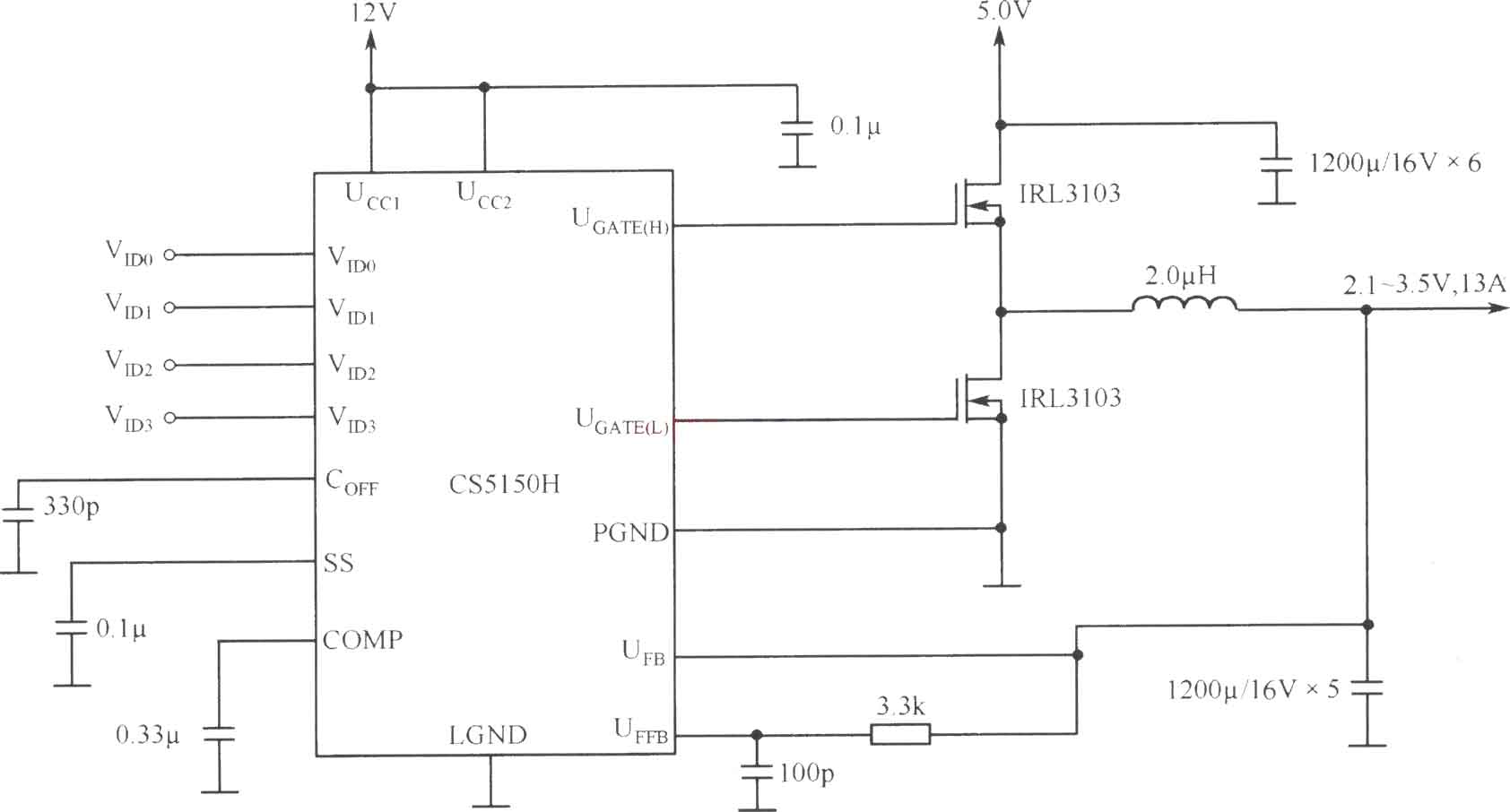

- 车辆正在采用越来越多的高级功能,包括自适应巡航控制、前方碰撞警告、自动远光灯控制、驾驶员监控、停车辅助、车联网 (V2X) 通信和完全自动驾驶。随着车辆提供越来越多的此类功能,它们需要相当大的处理能力,而现代高级驾驶辅助系统 (ADAS) 的电流可能超过 100 A。选择既能提供必要电压和电流,又能最大限度地减少电磁干扰 (EMI) 的处理器和电源可能会带来挑战。ADAS 片上系统Texas Instruments 的 TDA4VH-Q1 汽车片上系统 (SoC) 是一款适合用于 ADAS 应用的处理器。

- 关键字:

功能安全 ADAS 处理器 100A TI

- 4 月 2 日消息,英特尔公司副总裁,DCAI 事业群负责人 Karin Eibschitz Segal 在 Vision 2025 活动上表示,英特尔的目标是到 2026 年至强性能核与能效核产品将拥有具有竞争力的每瓦性能和无可争议的领导地位。根据英特尔目前披露的数据中心

CPU 产品路线图,下一代至强能效核产品 "Clearwater Forest" 将于明年上半年登场。该处理器最大核心数量将维持与

"Sierra Forest" 相同的 288 个,采

- 关键字:

英特尔 处理器 CPU

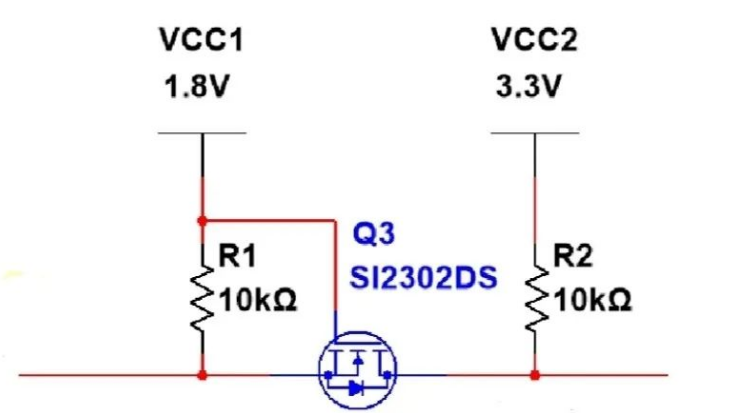

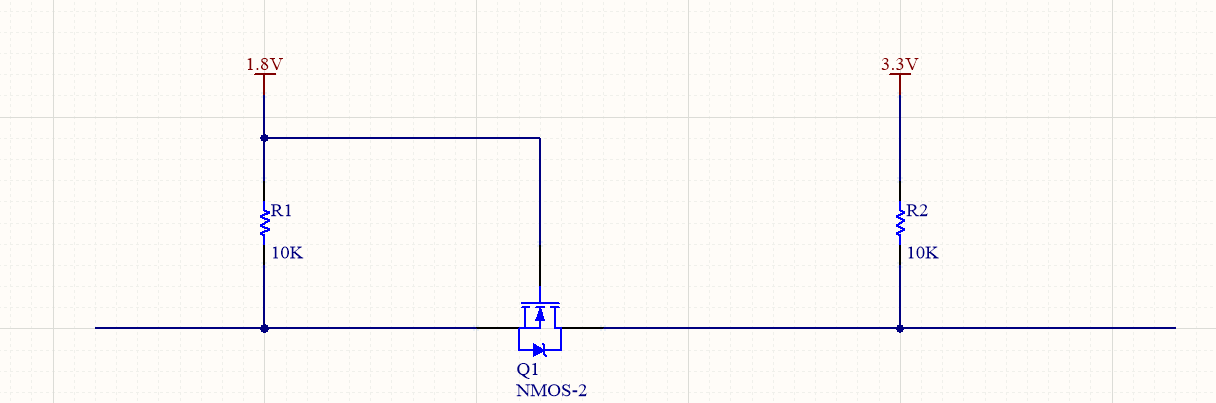

- 电源管理是工业应用的关键考虑要素,对系统性能、可靠性和成本效率有重大影响。 电源管理集成电路(PMIC)在调节电压和为系统内的各种组件(包括处理器和外设)供电方面发挥着至关重要的作用。创建高效的电源管理解决方案,需要深入了解应用的具体需求以及可用的技术和组件。 恩智浦提供全面且可扩展的能源管理解决方案,从电源插头到处理器,专为满足工业应用的特殊需求而设计。 恩智浦的PMIC具有多个关键的差异化优势,旨在高效地转换DC电源,为系统单芯片(SoC)或处理器及其相关外设供电。工业系统的安全稳健架构先进的可靠性、

- 关键字:

PMIC 处理器 工业应用

- 据 ChipHell 的消息来源AMD 即将推出的 Zen 6 处理器仍将与 AM5 兼容,但它们将引入一种新的基于小芯片的 CPU 设计,并显着增加台式机和笔记本电脑产品的内核数量。面向游戏玩家的高级处理器还将配备 3D V-Cache。AMD 基于 Zen 6 微架构的下一代 Ryzen 处理器将配备 12 核小芯片芯片 (CCD),如果链接的报告准确,这标志着 Zen 3/4/5 代处理器中使用的 8 核 CCD 的重大转变。因此,台式机 AM5 处理器将能够配备多达 24 个内

- 关键字:

AMD Zen 6 处理器

- 基于恩智浦的S32G2汽车网络处理器,艾睿电子开发出了一款功能强大的车载网关开发套件,助力开发者应对新一代汽车电子电气架构复杂性挑战。市场需求近几年,汽车电子电气架构迅速演进,包括更高的功能安全、信息安全、OTA能力、更强的通讯能力及网络带宽、更加智能的驾驶系统等。这些需求对芯片以及网络带宽提出了更高的要求。同时在电子设备越来越多、网络连接越来越多的情况下,功能安全和信息安全变得越来越重要。所有这些需求逐渐催生了新的汽车电子设计架构以及新的芯片解决方案。这些新的解决方案使得最新的汽车概念得以实现。随着这些

- 关键字:

恩智浦 汽车网络 处理器

处理器介绍

处理器是解释并执行指令的功能部件。每个处理器都有一个独特的诸如ADD、STORE或LOAD这样的操作集,这个操作集就是该处理器的指令系统。计算机系统设计者习惯将计算机称为机器,所以该指令系统有时也称作机器指令系统,而书写它们的二进制语言叫做机器语言。注意,不要将处理器的指令系统与 BASIC或PASCAL这样的高级程序设计语言中的指令相混淆。

指令由操作码和操作数组成,操作码指明要完成的操作 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473