首发推迟?台积电2nm真的用不起

苹果原本计划在今年推出的iPhone 17 Pro和iPhone 17 Pro Max两款机型上搭载台积电2nm处理器芯片,现如今可能会将时间推迟12个月至2026年。因此,将于今年下半年发布的iPhone 17系列中或将采用3nm的台积电N3P工艺,而非2nm制程。

本文引用地址:https://www.eepw.com.cn/article/202501/465987.htm

目前,台积电已在新竹宝山工厂开始了2nm工艺的试产工作(每月5000片晶圆的小规模生产),初期良率是60%,这意味着有将近40%的晶圆无法使用,每片晶圆的代工报价可能高达3万美元。

第一座工厂计划位于新竹县宝山附近,毗邻其专门为开发N2技术及其后续技术而建的R1研发中心,预计将于2025年下半年开始大批量生产(HVM)2nm芯片;第二座能够生产N2芯片的制造厂将位于高雄科学园区,该园区是高雄附近南台湾科学园区的一部分,HVM启动时间预计稍晚一些,可能在2026年左右。此外,台积电正在努力获得批准,在台中科学园区建造另一座具有N2能力的工厂。

2016年,制程技术演进至10nm后,报价增幅显著,达到6000美元;进入7nm、5nm制程世代后,报价破万;相比于2nm,目前3nm晶圆的价格大约在1.85-2万美元/片之间。

以iPhone 18 Pro系列首发搭载的A20 Pro处理器为例,这颗首个利用台积电2nm工艺制程的芯片,价格将由目前的50美元上涨至85美元,涨幅高达70%。由于先进制程报价居高不下,芯片厂商成本高企,势必将成本压力转嫁给下游客户或终端消费者。

2024年,高端智能手机集体用上了基于3nm工艺的旗舰芯片:骁龙8至尊版、天玑9400、A18系列都采用了台积电3nm工艺。相比4nm工艺,3nm工艺的代工费贵了不少,加上内存储存等核心元器件的涨价,让骁龙8至尊版/天玑9400旗舰机的价格普遍上涨。以小米为例,小米15的起售价,比上代就上涨了500元。

而2nm将如期在2025年进入量产,其量产曲线预计与3nm相似。台积电正全力提升产能,通过设施投资,预计到2026年台积电2nm制程产能将扩大至8万片晶圆。据报道,台积电已调整了对客户的2025年代工报价,以缓解海外设施高昂运营成本和2nm部署成本造成的毛利率损失的影响。

不可否认的是,高工艺的芯片确实带来了更高的性能和更低的功耗,但随之而来的高昂价格也让许多客户望而却步。而台积电之所以这么报价,当然是因为:没有对手。

台积电2nm工艺性能优秀

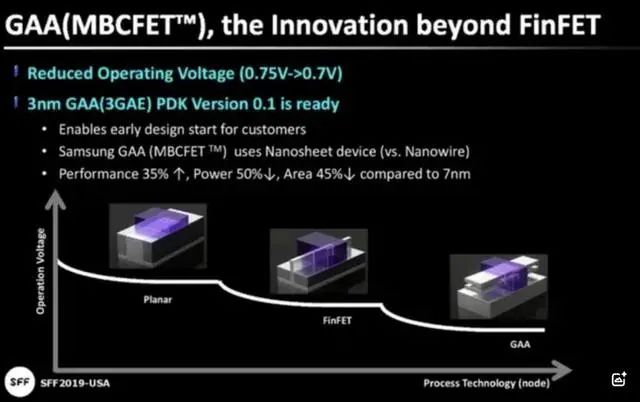

晶体管的密度越大,就必然需要沟道长度越来越小,而随着沟道长度的缩短,沟道管中的源极和漏极的距离也会越来越短。因此栅极很难再保证对沟道的控制能力,也意味着栅极电压夹断沟道的难度变大,即产生短沟道效应,从而出现严重的电流泄露。

为了解决这个问题,华人科学家胡正明在1999年提出了「鳍式场效应晶体管(FinFET)架构」。在这个结构中,栅门被设计成了类似鱼鳍状的3D结构,能够让晶体管沟道长度减少的同时,大幅减少电流泄露的问题。

FinFET架构的出现,让摩尔定律被续命将近20年,但自芯片代工行业进入先进制程后,该架构也开始逐渐失效,2nm的节点就被普遍认为是“决战节点” —— 全环绕栅极(GAA)纳米片晶体管被提出。与FinFET相比,GAA架构相当于将栅极的鳍片旋转90°,然后再在垂直方向上分成了多条鳍片,来增加其与沟道的接触面积。

这条技术路线得到了业内的广泛认可,但却让代工难度呈指数级上升。实际上,GAA技术在三星的3nm制程中就被抢先采用,但由于开发难度过大且时间紧迫,其3nm试生产的良率不足20%,根本无法满足量产需求,甚至无法自给自足。苹果、高通、联发科、英伟达等科技巨头都将3nm芯片的订单交给了台积电,台积电几乎包揽了全球的3nm芯片产能。

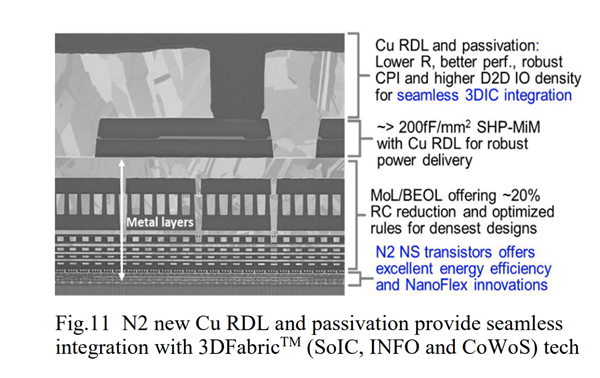

相比于三星的“一步到位”,台积电则选择在2nm工艺中首次引入GAA架构。此前在IEDM 2024大会上,台积电披露了N2工艺的关键技术细节和性能指标:对比3nm,晶体管密度增加15%,同等功耗下性能提升15%,同等性能下功耗降低24-35%。这一提升得益于GAA技术更低的阈值电压,从而降低了漏电功耗。

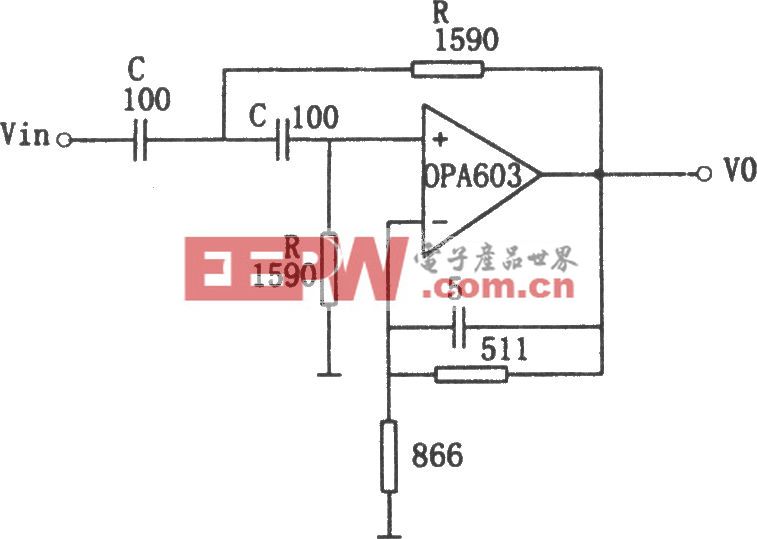

对比传统的FinFET晶体管:台积电N2工艺可以在0.5-0.6V的低电压下,获得显著的能效提升,可以将频率提升大约20%,待机功耗降低大约75%;还应用了全新的MOL中段工艺、BEOL后段工艺,电阻降低20%,能效更高;针对高性能计算应用,台积电2nm还引入了超高性能的SHP-MiM电容,容量大约每平方毫米200fF,可以获得更高的运行频率。

按照台积电的说法,28nm工艺以来,历经六代工艺改进,N2工艺单位面积的能效比已经提升了超过140倍。

同时,台积电还在研发N2P(N2增强版本),计划2025年完成资格认证阶段,2026年下半年量产。与原始N2相比,N2P功耗降低5%-10%(在相同频率和晶体管数量下)或性能提高5%-10%(在相同功率和晶体管数量下),并完全兼容N2。在欧洲开放创新平台论坛上台积电宣布,Cadence和Synopsys的所有主要工具以及西门子EDA和Ansys的仿真和电迁移工具,都已为台积电的N2P制造工艺做好准备。

整个N2系列将增加台积电的全新NanoFlex功能,该功能允许芯片设计人员混合和匹配来自不同库的单元,可以优化沟道宽度以提高性能和功率,然后构建短单元(以提高面积和功率效率)或高单元(以提高15%的性能)。

另外,还预计台积电将在2026年下半年开始量产A16制程(即1.6nm),A16工艺将结合台积电的超级电轨架构,即背部供电技术。与N2P工艺相比,A16在相同工作电压下速度快了8%-10%,或在相同速度下功耗降低15%-20%,同时密度提高至原来的1.1倍。

值得注意的是,因为台积电2nm的报价太高,高通已经在考虑使用三星2nm的工艺。相关报道称,高通在测试三星的2nm工艺,不过尚未敲定高通是否会将订单交给三星。毕竟在骁龙8+Gen1表现不俗之后,高通的骁龙8Gen2、骁龙8Gen3、骁龙8至尊版等旗舰芯片,都是由台积电代工。而且在骁龙8至尊版转向自研CPU架构后,CPU超大核主频达到了惊人的4.32GHz,功耗要求极高,现在确实是只有台积电才能做到。

AI应用的爆发式增长,让各大芯片厂商纷纷争抢台积电3nm的产能,台积电用十个月完成了2023年全年业绩。而且不难推测,所有3nm的客户都会在后续采用2nm制程。在这样的背景下,台积电董事长兼首席执行官魏哲家曾自信地表示,2nm工艺的需求空前高涨,目前2nm的规划产能已经超过3nm。

台积电N2还有对手吗?

2nm芯片的价格如此高昂,一方面是因为各个环节的成本都在上升,另一方面也是因为台积电在芯片代工行业中,已经形成了事实上的垄断。仅在今年,台积电便两次提高其代工费用,不仅是对3nm工艺制程,甚至5nm工艺制程的价格亦被提高4%-10%。

由于半导体设计企业在3nm以下的先进工艺中对台积电的依赖程度不断加深,而台积电产能不足、价格上涨,半导体设计企业对代工厂商多元化的意愿也在不断增强。那么在进入2nm工艺时代后,行业内还有能掣肘台积电的力量吗?

台积电的竞争对手三星正在全力提升2nm制程良率,并推动现有客户日本PFN等公司进行测试,以争夺2nm制程市场。三星在3nm工艺制程上跌了个大跟头后,立志要在2nm工艺制程上完成追赶。

此前业内就有传闻称,三星已经有暂停3nm工艺开发,全力“All in”2nm工艺的打算。业内人士透露,三星在其平泽P2和P3生产基地的4nm、5nm和7nm制程中,已有超过30%的代工生产线停产,并计划在年底前将停产比例扩大至约50%。而3nm的情况更不乐观,报道指出三星目前第一代的3nm制程工艺目前良率只有60%。

考虑到其位于华城的S3产线,在还未正式量产3nm晶圆前,就开始计划将设备升级为2nm工艺的配套设备,这种说法可能并非空穴来风。但按照三星的规划,其2nm产能至少要到2027年才能量产。

三星2nm工艺不仅要面对良品率较低的老问题,而且还要将性能功耗提升到客户所期望的水平,这可能是承受了数万亿韩元亏损的三星代工业务的最后机会。三星代工翻车是从高通骁龙888芯片出现了过热问题开始,这是由于当时三星的5nm工艺结合Arm的X1超大核心功耗过高导致的,因此从骁龙8+ Gen1开始,高通骁龙8系平台转投台积电。如果骁龙平台转向三星2nm工艺制程,那么其功耗问题将会是业内关注的热点。

另一边的英特尔,虽然已经完成18A工艺(等效2nm)的试生产工作,但被曝良率过低,且公司正处于动荡期,量产时间也是遥遥无期。台积电过于有统治力的市场主导地位在2nm制程上仍会延续。从目前的进度来看,先进制程的主要竞争者在2nm上依旧不能望其项背。

评论