EUV掩膜版清洗—Intel的解决之道

对于极紫外(EUV)光刻技术而言,掩膜版相关的一系列问题是其发展道路上必须跨越的鸿沟,而在这些之中又以如何解决掩膜版表面多层抗反射膜的污染问题最为关键。自然界中普遍存在的碳和氧元素对于EUV光线具有极强的吸收能力。在Texas州Austin召开的表面预处理和清洗会议上,针对EUV掩膜版清洗方面遇到的问题和挑战,Intel Corp. (Santa Clara, Calif.)的Ted Liang主持召开了一次内部讨论,并在会上向与会的同仁报告了在这一领域Intel和Dai Nippon Printing Co. Ltd. (DNP, Tokyo)合作研究的成果。

本文引用地址:https://www.eepw.com.cn/article/86296.htmEUV光刻技术被普遍认为是实现32nm乃至更高技术节点CMOS关键工艺层的主要光刻技术方案。尽管对于分辨率而言EUV光刻技术使用的曝光波长比目前使用的ARF光刻技术缩小了10倍多,但是由于EUV波段的光线极易被各种光学材料吸收,这也需要研发一套全新的掩膜版结构以满足使用需求。因此,相对于目前的投影式光学系统而言,EUV掩膜版将采用反射技术而非折射技术。

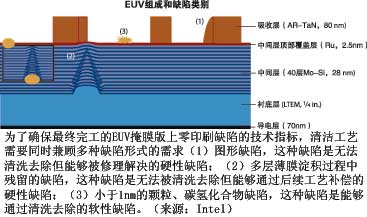

Liang的报告主要集中在如何在掩膜版清洗后实现零缺陷增长,在掩膜版清洗技术各项指标中这是非常困难的。通过对Intel的标准EUV掩膜版剖面结构的分析,他指出,为了达到零印刷缺陷的完美标准,掩膜版清洁技术需要同时兼顾无法清洗去除的硬性缺陷和可清洗去除的软性缺陷两方面的需求。

尽管EUV掩膜版清洗步骤远远少于硅片半导体的生产流程,但是这也绝非易事,它的挑战包括:

■对于硅片清洗而言,其颗粒移除率(PRE)不需要达到100%,但对于掩膜版而言却并非如此,其原因是对于产品良率而言,掩膜版表面颗粒的影响更大。

■如同硅片半导体制造工艺那样,清洗过程中引起的EUV掩膜版表面损伤和薄膜损耗越来越关键。

■与193nm掩膜版相比,EUV掩膜版引入了包括中间层顶部覆盖层钌和吸收层TaN在内的多种新材料。

■EUV掩膜版对于氧化和污染非常敏感。

■由于零成像缺陷是可以实现的,在工厂内用于生产的掩膜版需要经常清洗。

■对于掩膜版清洗而言,关键是移除有机物而不能氧化中间层顶部覆盖层钌材料表面。

Liang指出在6英寸钌/多层淀积材料(Ru/ML)的表面完全移除颗粒是确实可行的,但难度在于整个清洗工序需要确保无副产物残留在掩膜版表面。和DNP的合作研究表明,副产物的数量与材料表面的性质和粘附度相关。对于193nm光刻技术所使用的石英材料而言,由于其具备非常低的黏附力,故对于副产物是“免疫”的,而同样用于193nm光刻技术的铬材料其表面的黏附力也较低,所以清洗后表面黏附的副产物数量也较低,进而不会影响成像质量。但对于EUV的Ru/ML表面情况就截然不同了,它们不仅会黏附更多的副产物,而且由于副产物对EUV光线的吸收效应,因此会对成像质量产生较大的影响。

更糟糕的是,由于副产物为有机物,它们无法通过额外的扫描探针显微(SPM)化学处理移除。可能的解决方案是改变清洗材料,比如采用能够有效移除有机物的臭氧水,或者进一步增强过滤效率,从而能在源头减少副产物的数量。

在Liang的报告中提到了Pall Corp. (East Hills, N.Y.)正致力于研发新一代的过滤装置,Sematech Albany也在研发一些移除硬性颗粒的技术手段。对于使用臭氧去离子水(DIO3),Liang介绍其中主要存在的问题是如何避免对掩膜版表面的腐蚀损伤。经过20分钟的清洗,表面被损伤了。尽管DIO3是非常具有吸引力,也非常易于操作,但对掩膜版表面的损伤却是一个问题。

评论