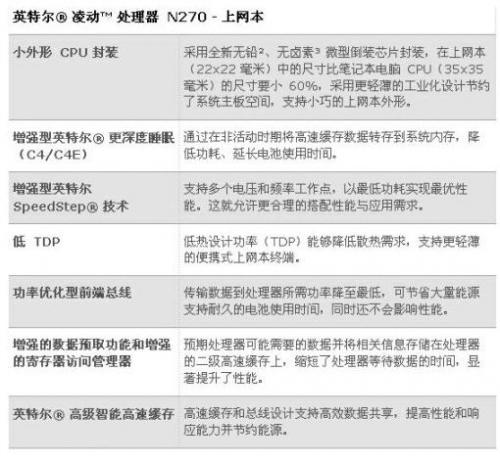

重建英特尔:代工与 IDM 数十年的问题被揭开

英特尔作为唯一的主要集成设计制造商 (IDM) 在半导体行业中拥有独特的地位,这意味着他们作为一家公司设计和制造自己的先进芯片。虽然三星拥有这两种功能,但 LSI(设计)和代工厂之间实际上存在一道墙。英特尔作为 IDM 的独特地位既是一个主要的结构优势,也是一个劣势。

本文引用地址:https://www.eepw.com.cn/article/202306/447936.htm从理论上讲,由于是一家数据共享限制较少的单一公司,英特尔可以比 AMD 等竞争对手与台积电更紧密地优化彼此的制造和设计。他们的最终芯片定价可以低于 AMD,因为无需支付外部台积电代工税。

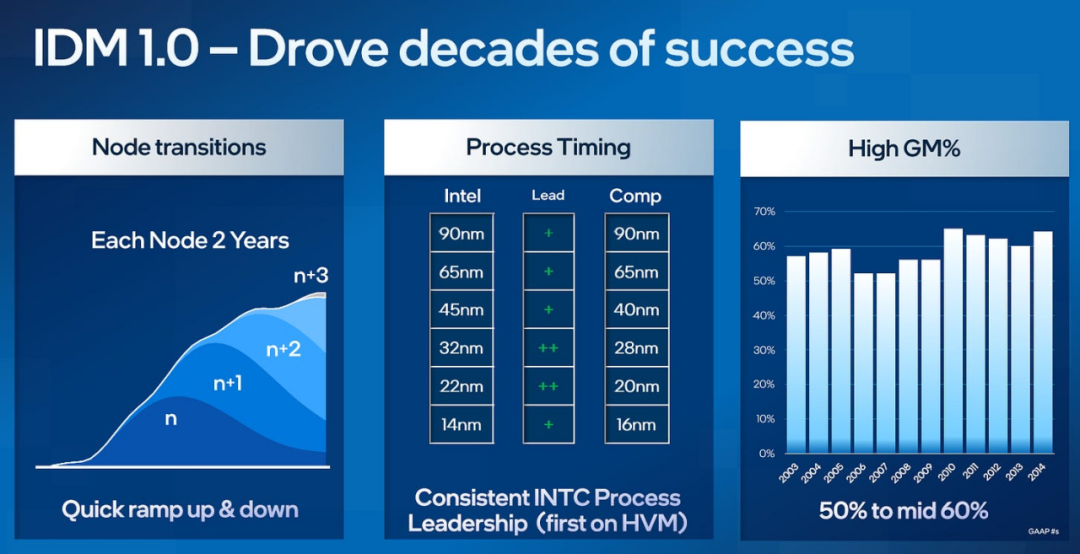

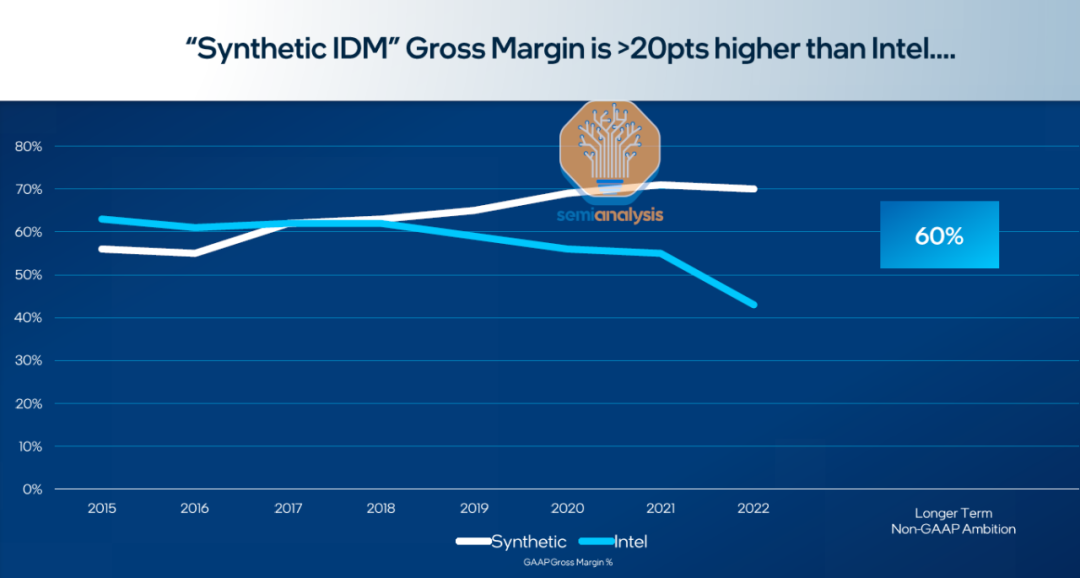

几十年来,这个模型一直有效。英特尔在工艺节点上领先于所有竞争对手,因此能够占据主导地位。他们的利润率始终高于台积电和 AMD 等公司。下图显示了如果假设代工厂 + 无晶圆厂公司与英特尔是同一家公司,那么它们会是什么样子。

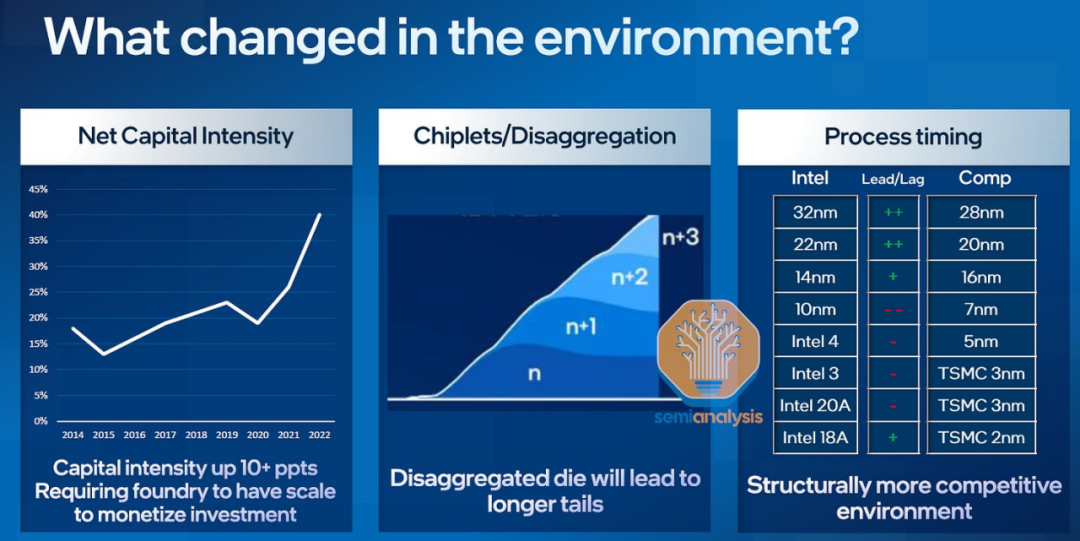

工艺节点优势在 2010 年代初的 14 纳米工艺中开始出现裂痕,但在原定于 2016 年进行的 10 纳米工艺过渡时完全崩溃。代工厂在 16 纳米、10 纳米和 7 纳米工艺上竞相领先,超越了英特尔 3 年的领先优势,并扭转了颓势。

原因有一部分是由于大型 IDM 造成的。责任和问责没有适当地落实到各个团队和业务部门。英特尔的某些部门逐渐衰落,在性能或成本方面落后于行业,但没有人能说清楚,因为英特尔处于自己的压倒性工程主导地位。

一旦英特尔失去了领先地位,效率低下的问题就变得显而易见。如今,英特尔制造晶圆的效率明显低于台积电。由于工具利用率较低且良率较差,英特尔需要更多的晶圆厂空间来实现相同的产量。

与此同时,英特尔的设计团队明显落后于 AMD,需要更大的内核和更多的晶体管,消耗更多的功率才能实现类似的性能。此外,由于设计方法较差,英特尔的设计团队需要更长的时间和更高的成本才能实现新架构的生产。

英特尔针对这些问题的解决方案之一是通过快速连续缩小两次(英特尔 4/3 和英特尔 20A/18A)来赶上工艺节点。但仅靠这一点并不能解决问题,因为它们仍然缺乏规模、客户群和运营效率。

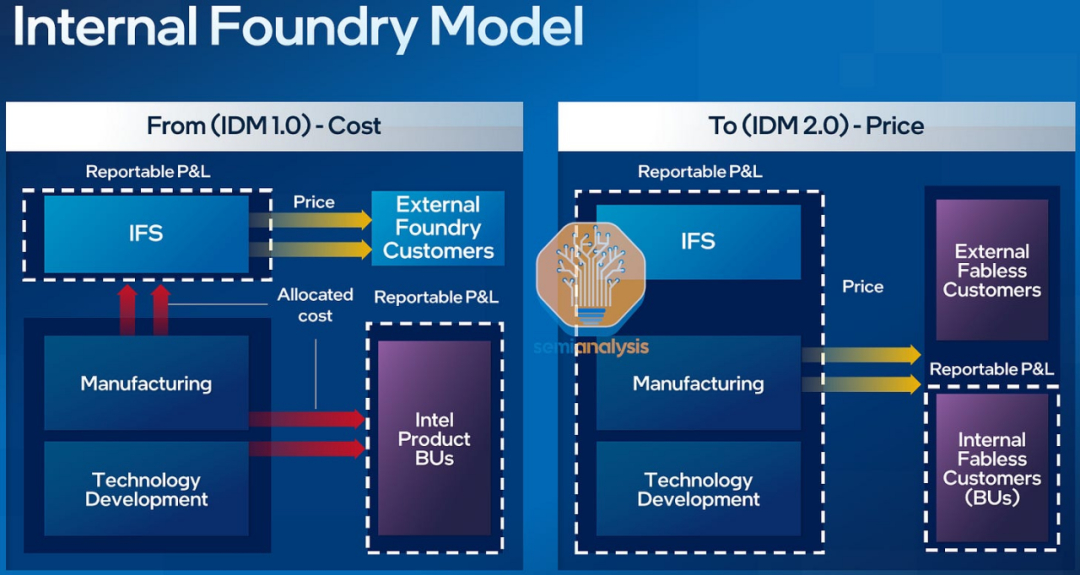

英特尔目前正在尝试解决其中许多问题,并转型成为各种外部客户的外部代工厂。虽然从表面上看,这只有在他们能够赢得外部客户的情况下才有帮助,但还有其他优势。

通过转向内部代工模式,英特尔可以开始结束将成本分配给整个业务部门而不是单个设计和团队的无意义做法。这将通过将责任降低到较低水平来帮助解决他们的一些主要低效率问题,这将有助于管理产品和晶圆厂级别的成本。

当前效率低下

这些各种各样的问题是压倒性的,并导致了我们今天看到的英特尔。一般来说,英特尔产品团队可以隐藏在其制造实力背后,而对分配给整个业务部门的成本不予理睬。

在半导体制造中,晶圆是分批制造的,称为批次。这些批次是晶圆的集合,在继续使用下一个可用的工具进行制造之前,由工具按顺序处理这些晶圆。由于一座晶圆厂的成本高达数百亿美元,因此必须最大限度地利用晶圆厂的工具。一般来说,由于晶圆分批,前沿晶圆的处理时间可能需要 10 周。

另一方面,如果不考虑成本,先进的晶圆也可以在几周内加工完成,但这会导致工具不断等待晶圆以便尽快加工,从而导致效率极大低下。这称为「热批次(hot lot)」,指的是比标准批次优先且处理速度更快的一批晶圆。

他们可以做任意数量的热门批次,可以做任意数量的样品。

大卫·津斯纳 (David Zinsner),英特尔首席财务官表示,这可能有多种原因,例如加快新工艺步骤或工具的验证,或者为新设计或技术创建测试芯片。该术语源于这样的想法:这些晶圆是「热的」,因为它们被尽可能快地推进制造过程。

「我们确实使用了很多热门方法。通常,作为一名总经理,我并不总是像我应该的那样认真思考热门批次的成本——不仅仅是成本,还有工厂利用率和效率方面的中断。」Sandra Rivera,英特尔数据中心和人工智能事业部执行副总裁兼总经理说,然而,运行热批次确实会降低设备利用率和整体晶圆厂效率。因此,这是快速处理特定晶圆的紧迫性与制造工厂的整体效率和吞吐量之间的权衡。

「我们的基准测试表明,我们的材料速度比业内同行快 2 到 3 倍,预计总产量会受到 8% 到 10% 的影响。」Jason Grebe 是英特尔企业规划集团副总裁兼总经理,Jason Grebe 也表示英特尔正在解决这个问题。方法是转向内部代工厂模式,并向业务部门收取热门批次的费用,就像任何其他代工厂向客户收取这些热门批次的费用一样。

英特尔相信,仅这一改变就可以每年为他们节省 5 亿至 10 亿美元。

步骤和样品

设计芯片的成本非常高。一旦有了完整的设计,将其投入生产需要将设计发送到晶圆厂,将这些设计转换为数十个物理光掩模以放置在光刻工具内,并通过数千个工艺步骤运行测试芯片。一旦收到测试芯片,就可以检查它们是否存在错误/问题,并且可以调整设计。

但目前英特尔的主要劣势之一是它们需要更多的迭代。步进是指将修改后的设计发送到晶圆厂,并为新的测试芯片创建新的光掩模。

他们可以按照自己的意愿进行任意多的步数。

大卫·津斯纳 (David Zinsner),英特尔首席财务官说英特尔花了很多力气才将 Sapphire Rapids 推向市场,而 AMD 通常只需要相对比一小部分的力气才能将 Genoa 等竞争芯片带到市场。这使得英特尔制造所有这些额外光掩模的成本大幅增加,并大大增加了将新设计推向市场的时间。

我们甚至听到前员工传言,曾经有一段时间,一些英特尔设计团队宁愿将设计发送到晶圆厂,拿回大量样品,并测试其是否存在错误,而不是通过模拟和验证来完成更多工作。

英特尔计划通过减少样本和步进的数量来解决这个问题,方法是向设计和产品业务部门收取这些操作的合理价格,而不是允许任意数量的步进。几年前,设计团队开始转向更符合行业标准的设计方法,尽管这项任务艰巨。

测试、排序、分类

芯片制造出来后,会对其进行测试和分类,以排除故障并进行各种分类以进入不同的产品。多年来,英特尔一直是测试、排序和装箱领域的先驱。他们的工具是高度定制的,并且有许多独特的内部测试模式。虽然这给英特尔带来了一些相对于行业的优势,但并不都是积极的。

Jason Grebe,英特尔企业规划集团副总裁兼总经理说:「与业界同行相比,我们测试时间越来越长。目前,我们估计我们的测试时间是竞争对手的 2 到 3 倍。实际上,我们的低成本测试平台正在补贴我们测试时间的增长。」

英特尔过去拥有的巨大制造能力优势,再次变成了劣势。鉴于最终芯片的现场可靠性并没有真正差异化,测试时间没有必要是 AMD 等竞争对手的 2 到 3 倍。

英特尔认为,更直接地向业务部门收取测试、分类和分类费用将使业务部门更加清楚他们在设计中使用的测试策略,并每年节省约 5 亿美元。

此外,英特尔先进的分箱策略导致他们制定了我们称之为「SKU 垃圾邮件」的产品策略。在 PC 和数据中心领域,英特尔拥有数十种 SKU,因为他们能够将芯片分类到最终终端市场芯片的众多箱子中。与 AMD、Broadcom 和 Nvidia 的产品堆栈要简化得多相比,通过减少 SKU 的数量显然有节省成本的潜力,但我们还没有听说英特尔有任何改变这一点的计划。

评论