3D DRAM技术是DRAM的的未来吗?

5月25日,有消息传出,华为将在VLSI Symposium 2022期间发表其与中科院微电子研究所合作开发的 3D DRAM 技术。随着“摩尔定律”走向极限,DRAM芯片工艺提升将愈发困难。3D DRAM就成了各大存储厂商突破DRAM工艺极限的新方案。

DRAM工艺的极限

目前,DRAM芯片最先进的工艺是10nm。据公开资料显示,三星早已在2020年完成了10nm制程DRAM的出货;美光和SK海力士也在2021年完成了10nm DRAM产品的量产。

那么,10nm是DRAM工艺的极限吗?

在回答这个问题之前,我们先来看看DRAM工艺的发展历程。如图1所示,DRAM的工艺不是直接从20nm一下到10nm。而是在20nm之后,又细分成了1Xnm(16nm-19nm)、1Ynm(14nm-16nm)、1Znm(12nm-14nm)、1anm(10-12nm)。可以看出,在20nm之后,DRAM工艺的提升的确越来越难,缩小2nm,就意味着前进了一大步。

图1 内存厂商路线图(来源:前瞻研究院)

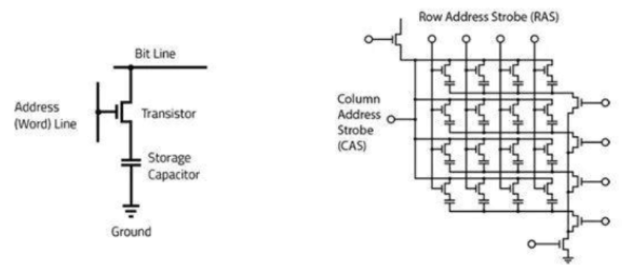

DRAM工艺提升困难的原因,主要在于它的结构。DRAM是基于一个晶体管和一个电容器的存储单元。DRAM扩展就是在一个平面上,将每个存储单元像拼图一样拼接起来。要想提升DRAM工艺,电容器的缩放是一个挑战。另一个挑战是电容到数字线的电荷共享,要考虑用多少时间将电荷转移到数字线上、数字线有多长。

图2 单个存储单元和阵列(来源:网络)

或许10nm并不是DRAM的极限,但是DRAM工艺提升的脚步正在放缓。人们迫切需要一个新方案,来继续提升DRAM的性能。

在一个平面内塞入更多存储单元很困难,那么将多个平面叠起来行不行?这就是3D DRAM,一种将存储单元堆叠至逻辑单元上方的新型存储方式,可以实现单位面积上更高的容量。

有哪些厂商在布局3D DRAM?

3D DRAM作为目前最被看好的下一代DRAM方案,有不少内存厂商已在布局。其中就有被大家熟知的内存巨头——三星、美光。据BusinessKorea报道,三星今年已经开始开发一种层叠单元的技术。与高带宽内存(HBM)不同的概念,是通过将多个模具堆叠在一起产生的。与此同时,美光也提交了一份3D DRAM的专利申请。与三星不同,美光的方法是在不铺设单元的情况下改变晶体管和电容器的形状。

而这次爆出的华为3D DRAM技术,据透露,是基于铟镓锌氧 IGZO-FET材料的 CAA 构型晶体管 3D DRAM 技术,具有出色的温度稳定性和可靠性。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。