据报道三星押注4-7纳米工艺,价格比台积电高出30%,瞄准中国尚未进入的市场

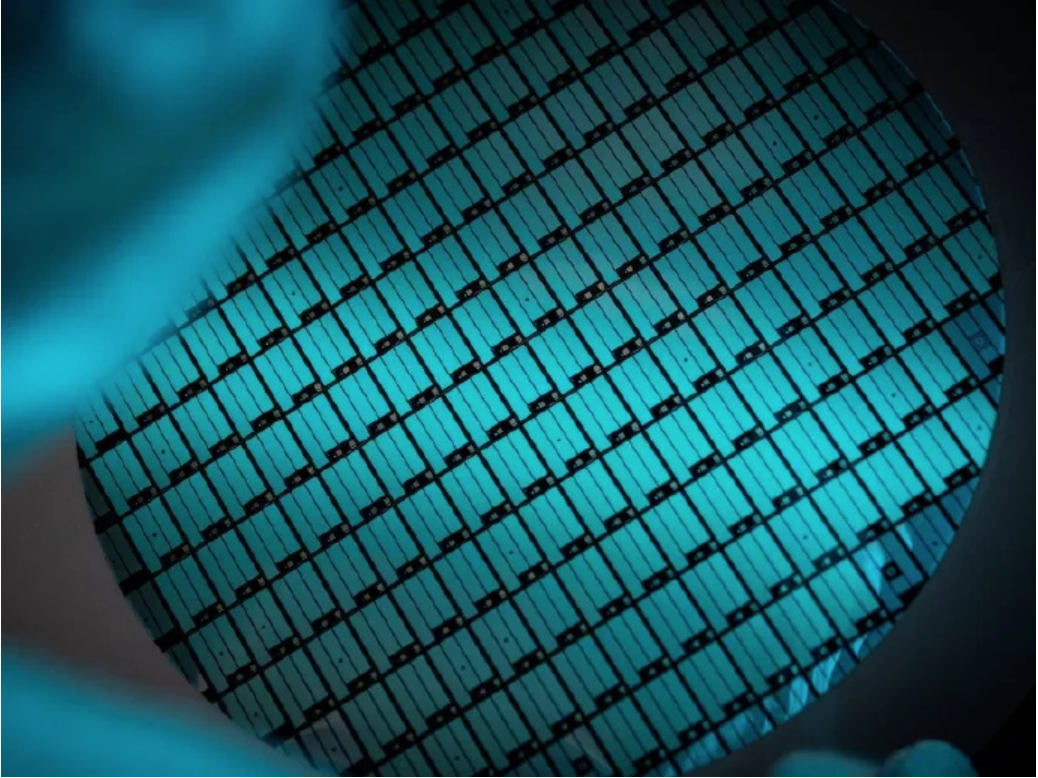

虽然英特尔已从 18A 转向 14A 进行战略权衡,据报道三星通过优先考虑 2 纳米和 4 纳米而不是 1.4 纳米做出了妥协,根据 ZDNet。同时,Chosun Biz 透露,这家陷入困境的半导体巨头还计划通过将这些节点的价格定价比台积电低约 30%来提高 7 纳米以下工艺的需求——这仍然是中国竞争对手无法企及的领域。

Chosun Biz 报道称,三星的 4 纳米工艺旨在通过 SF4U 提升约 20%的能效来赢得订单。据三星称,SF4U 是一款高端 4 纳米变体,采用光学缩小技术来提升 PPA(功耗、性能和面积),计划于 2025 年实现量产。

尽管三星的 4 纳米、5 纳米和 7 纳米工艺在芯片性能上落后于台积电,但该公司通过将价格降低约 30%并在激烈的价格战中保持 70%以上的良率来竞争,报告指出。据 Chosun Biz 援引一位行业内部人士的话称,三星的 4 纳米和 5 纳米工艺已经改进到足以与台积电抗衡,这使其在尚未开发这些工艺的中国竞争对手面前获得了关键优势。

亚2纳米更新

同时,Chosun Biz 报道说,尽管三星的亚 3 纳米芯片良率已超过 40%——足以实现量产——但该公司仍在努力争取亚 3 纳米芯片的大订单。与英伟达和高通的初步评估未能达到预期,促使该公司将重点从急于生产 1 纳米工艺转移到提高当前节点的性能,报告补充道。

根据 etnews 报道,三星在 7 月 1 日 SAFE 论坛上宣布,将 1.4 纳米量产计划推迟两年——现计划于 2029 年推出,而非原计划的 2027 年。

相反,Chosun Biz 建议,三星计划通过引入第三代(SF2P+)节点来推进其 2 纳米工艺,明年将整体性能提升超过 20%。

评论