解密英特尔最新制程路线,与主流先进制程有何区别?

7月27日,英特尔召开制程工艺和封装技术线上发布会。会上,英特尔CEO帕特·基辛格表示,英特尔正在通过半导体制程工艺和封装技术来实现技术的创新,并公布有史以来最详细的制程工艺和封装技术发展路线。

本文引用地址:https://www.eepw.com.cn/article/202108/427297.htm英特尔表示在10月27日的Intel Innovation上还会有更多重要消息放出。

采用全新命名体系

芯片制程工艺节点名称是以晶体管的栅极长度来命名,然而现如今整个行业对于芯片工艺节点的命名开始多样化,这些多样的方案既不再指代任何具体的度量方法,也无法体现如何能够实现能效和性能的平衡。因此,英特尔从性能、功耗和面积等各方面进行了综合考虑,对芯片制程工艺采用新的命名体系。

在发布会上,英特尔公布了未来5年芯片制程的技术路线图,并采用了新的命名体系,分别是Intel 7(此前称之为10纳米Enhanced SuperFin)、Intel 4(此前称之为Intel 7纳米)、Intel 3以及Intel 20A。

而这一举动则是为了在制程规格的名称上与跟台积电、三星保持对等关系。

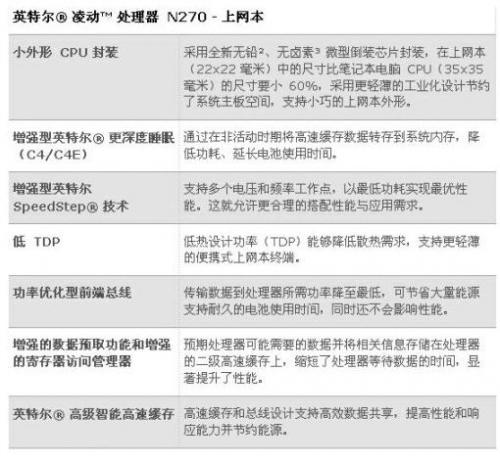

· Intel 7:工艺拥有最佳的FinFET的晶体管,与Intel 10nm SuperFin相比,每瓦性能将提升大约10%~15%。Intel 7的优势包括更高的应变能力、更低的电阻材料、更新型的高密度刻蚀技术、拥有流线型结构以及采用更高的金属堆栈来实现布线优化。据了解,于2021年推出的面向客户端的Alder Lake,以及预计将于2022年第一季度投产的面向数据中心的Sapphire Rapids将会采用Intel 7工艺。

· Intel 4:将完全采用EUV光刻技术,可使用超短波长的光来刻印极微小的图样。与Intel 7相比,Intel 4的每瓦性能将提高约20%。据了解,Intel 4将于2022年下半年投产,2023年出货,将会应用在面向客户端的Meteor Lake和面向数据中心的Granite Rapids。

· Intel 3:随着FinFET技术的进一步优化,以及EUV技术使用的不断完善,将实现与Intel 4相比每瓦性能约18%的提升,在芯片面积上也将会有改进。据悉,Intel 3将于2023年下半年开始在相关产品中使用。

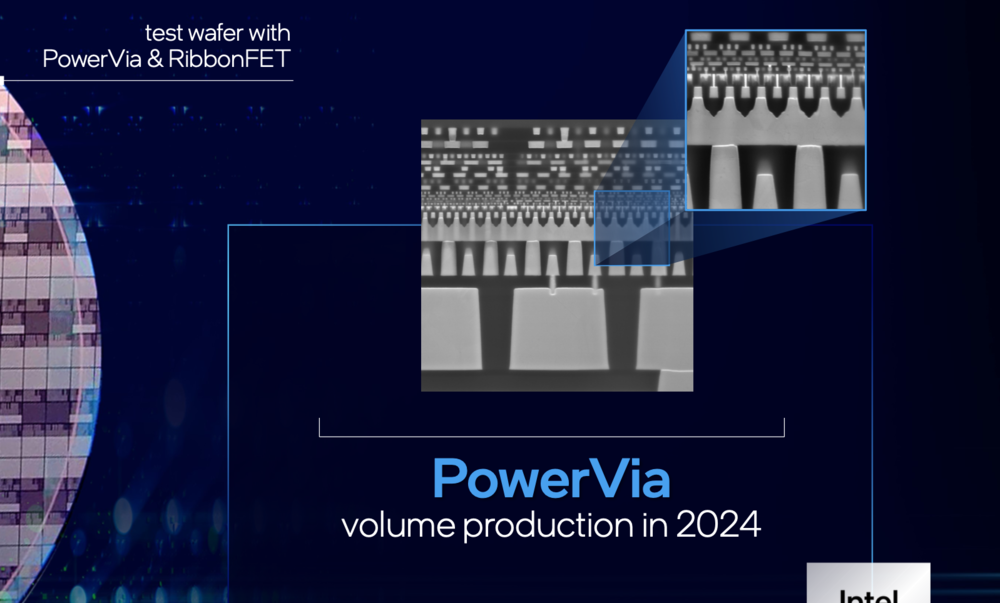

· Intel 20A:在Intel 3工艺后,芯片制程将会越来越接近1纳米节点,进入更微小的埃米时代。因此,Intel 3之后的工艺,英特尔也改变了命名方式,命名为Intel 20A。Intel 20A将凭借RibbonFET和PowerVia两大突破性技术开启埃米时代。Intel 20A预计将在2024年推出,且在此制程工艺技术中,英特尔将会与高通公司进行合作。而近期,英特尔也刚刚宣布与高通签订协议,将为高通提供代工服务,而这或许也是英特尔向Intel 20A技术迈进的关键一步。

实话讲,英特尔最有趣且最应该受到关注的产品,毫无疑问是Intel 3之后的Intel 20A。当然,Intel 4将作为第一批应用阿斯麦高数值孔径(High-NA)极紫外辐射光刻技术(EUV)的处理器也倍受瞩目,但象征意义不如Intel 20A。

Intel 20A(5nm)之所以被英特尔称为历史上制程技术发展的下一个分水岭,是因为它是第一块应用英特尔两大“开创性技术”的芯片:

· 替代FinFET的全新晶体管架构 Gate-All-Around(英特尔把它命名为RibbonFET);

· 能够解决“互联瓶颈”的电能传输系统PowerVia:是英特尔全新的背面电能传输网络。这是由英特尔工程师开发的一项独特技术,也将在Intel 20A中首次采用。

我们知道,现代电路的制造过程从晶体管层M0作为最小层开始。在此之上,以越来越大的尺寸添加额外的金属层,以解决晶体管与处理器不同部分(缓存、缓冲器、加速器)之间所需的所有布线。现代高性能处理器的设计中通常有10到20个金属层,顶层放置外部连接。然后将芯片翻转(称为倒装芯片),以便芯片可以通过底部的连接和顶部的晶体管与外部世界进行通信。

这种传统的互连技术是在晶体管层的顶部进行互联,由此产生的电源线和信号线的互混,导致了布线效率低下的问题,会影响性能和功耗。为此业界转向了“背面供电的技术”,也就是英特尔所说的PowerVia。

在新的工艺中,英特尔把电源线置于晶体管层的下面,换言之是在晶圆的背面。通过消除晶圆正面的电源布线需求,可腾出更多的资源用于优化信号布线并减少时延。通过减少下垂和降低干扰,也有助于实现更好的电能传输。

换另一种说法,在全新的设计中,英特尔现在将晶体管置于设计的中间。在晶体管的一侧放置了通信线,允许芯片的各个部分相互通信。另一方面是所有与电源相关的连接(以及电源门控)。从本质上讲,英特尔转向了三明治,其中晶体管是填充物。

PowerVia将是业界首个部署的背面电能传输网络。

英特尔动作不断

几十年来,英特尔在芯片制程工艺方面一直处于领先地位,但是近几年随着市场竞争的愈发激烈,英特尔逐渐失去了很多优势。

技术创新层面遭遇的危机也蔓延至他们的财务数据上,从2020年Q1到2021年Q3,英特尔净利润连续3个季度下滑;而历来作为数据中心市场的绝对王者,英特尔这一业务板块的收入也在三个季度内持续下降。

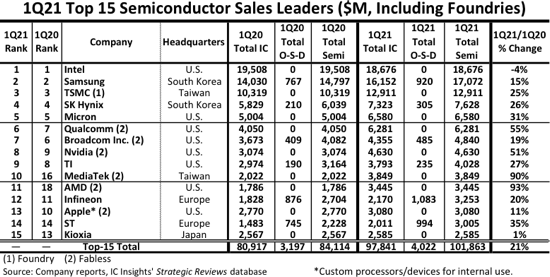

2021年5月,权威市场调研机构IC Insight发布的《2021年Q1全球Top15半导体公司业绩与排名》指出,英格尔虽然位列第一,但却是所有厂商中唯一一家营收下滑的企业。

为此,英特尔开始重振旗鼓,表示在2025年之前重返产业巅峰。为了达到这一目标,英特尔在芯片制程方面可谓是下足了功夫。

英特尔在芯片制造领域将迎来十年来的首个新设计:放弃了FinFET工艺,转向了GAA晶体管。

与FinFET不同的是,在FinFET中,较高电流需要多个并排的鳍片;GAA晶体管的载流能力主要是通过垂直堆叠几个纳米片(上图),而栅极材料主要是包裹在沟道周围来提高的。纳米片的尺寸可以按比例缩放,以便晶体管可以按照要求的特定性能进行调整。

另外制定了和高通联手打造芯片这个大胆的计划,今年5月的时候帕特·基辛格还表示,英特尔要在技术上超越台积电,并为此要升级墨西哥的Fab 11X工厂。该工厂于1996年建成,主要生产45纳米和32纳米制程,在芯片领域属于中低端产品,升级后很可能会成为上文提到的20A产品生产线。

2010年后,英特尔平均每5年开设一个新处理器芯片工厂 —— 从2010年到2021年,英特尔仅建造了两个处理器芯片工厂:Fab 42和D1X。而帕特·基辛格上任还不到半年,就宣布 2023 年将要建成位于爱尔兰的 Fab 34 以及 Fab 11X。

评论