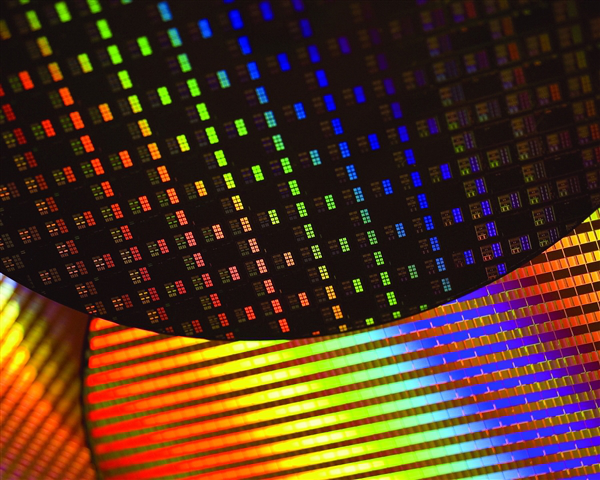

三星即将宣布3nm以下工艺路线图 挑战硅基半导体极限

在半导体晶圆代工市场上,台积电TSMC是全球一哥,一家就占据了全球50%以上的份额,而且率先量产7nm等先进工艺,官方表示该工艺领先友商一年时间,明年就会量产5nm工艺。在台积电之外,三星也在加大先进工艺的追赶,目前的路线图已经到了3nm工艺节点,下周三星就会宣布3nm以下的工艺路线图,紧逼台积电,而且会一步步挑战摩尔定律极限。

本文引用地址:https://www.eepw.com.cn/article/201905/400429.htm在半导体工艺上,台积电去年量产了7nm工艺(N7+),今年是量产第二代7nm工艺(N7+),而且会用上EUV光刻工艺,2020年则会转向5nm节点,目前已经开始在Fab 18工厂上进行了风险试产,2020年第二季度正式商业化量产。

明年的5nm工艺是第一代5nm,之后还会有升级版的5nm Plus(5nm+)工艺,预计在2020年第一季度风险试产,2021年正式量产。

三星这边去年也公布了一系列路线图,而且比台积电还激进,直接进入EUV光刻时代,去年就说量产了7nm EUV工艺,之后还有5nm工艺,而3nm工艺节点则会启用GAA晶体管,通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。

3nm之后呢?目前台积电、三星甚至Intel都没有提及3nm之后的硅基半导体工艺路线图,此前公认3nm节点是摩尔定律最终失效的时刻,随着晶体管的缩小会遇到物理上的极限考验。

三星将在5月14日举行2019年度的SSF晶圆代工论坛会议,消息称三星将在这次会议上公布3nm以下的工艺技术,而三星在这个领域的进展就影响未来的半导体晶圆代工市场格局。

评论