从头到尾构建混合信号高集成度系统(SoC)的步骤(6):布局

Tamara博士: 嗨,Dave,你坐在那儿干什么?

本文引用地址:https://www.eepw.com.cn/article/142795.htmDave:坐在他办公室地板上,正在吸吮一杯溢到杯口的咖啡,嗨,Tamara博士,正在清理房间……太不好意思叫服务人员了。

Tamara博士:[挨着Dave坐下来,拿起几张纸巾动手帮忙] 我知道你是什么意思。清理地板(floor work),趁机活动活动。这提醒我,我们可以进行下一次讨论了。

Dave:这有何关联?

Tamara博士:我们需要讨论设计布局,我想那也是从平面图规划(floor planning)开始的。

Dave:是的,平面图规划。首先,我本人并不是布局方面的专家。我只是偶尔帮个小忙,但如今的工具和工艺相当复杂,所以要布置芯片就离不开能干的布局人员。实际上,他们的正式头衔是‘掩膜设计人员’,因为他们的工作成果是利用数据去制作用于生产芯片的掩膜。

Tamara博士: 掩膜设计人员知道芯片的工作原理吗?我的意思是,他们如何知道如何开始,哪些模块重要而哪些不重要?

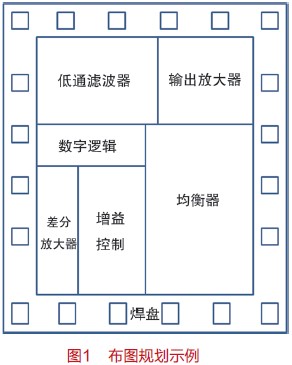

Dave:掩膜设计人员知道有关工艺和软件的许多知识,但通常在他/她开始时并不怎么了解某一个特定的芯片。所以我们要进行平面图规划。但在此之前,我们也能分层级地构建我们的原理图,以便这些模块在原理图中得到清楚的显示。然后平面图规划变为简单的画线工作,来标明模块的位置。请看图1。

Tamara博士: 我明白了。你从原理图绘制出芯片内部的简单平面功能图。但作为非布局专家,你如何知道模块在芯片上占多大面积?

Dave:我想我的猜测是有根据的。我使用足够多的布局工具来大致推断模块的尺寸,我的布图规范就建立在这个基础之上。我们对模块进行面积预算,然后掩膜设计人员会在布图规划中参与进来并让我知道事情是否对头。电路设计人员和掩膜设计人员是相互协同工作的。

Tamara博士:所以重要的是保持良好的工作关系。

Dave:是的,但有时这是一个挑战。我们总想在所有最终仿真完成前开始布局工作。实际上,最终仿真必须包括合理布局后产生的寄生参数,所以我们直到布局接近完成时才能进行最终仿真。

Tamara博士:这对掩膜设计人员有何影响?

Dave:一言以蔽之:改动。掩膜设计人员喜欢我们尽早固定电路设计不再改动,以便他们能够优化布局。但后面的仿真可能会显示出我们需要纠正的问题。所以最终,掩膜和电路设计人员都必须能灵活改变他们的设计。

Tamara博士:明白了!一旦你有了一个基本平面布图规划,掩膜设计人员肯定还需要其他信息。

评论