UALink规范推出打响撼动英伟达AI统治的第一枪

UALink 的主要目标之一是为 AI 加速器提供有竞争力的连接生态系统,该技术将与 Nvidia 成熟的 NVLink 技术相媲美,该技术使这家绿色公司能够构建机架级 AI 优化解决方案,例如 Blackwell NVL72。随着 UALink 1.0 的出现,AMD、Broadcom、Google 和 Intel 等公司也将能够使用行业标准技术而不是 Nvidia 的专有解决方案来构建类似的解决方案,这意味着成本更低。

Ultra Accelerator Link Consortium 周二正式发布了最终的 UALink 1.0 规范,这意味着该小组的成员现在可以继续对支持新技术的实际芯片进行流片。新的互连技术面向 AI 和 HPC 加速器,并得到包括 AMD、Apple、Broadcom 和 Intel 在内的众多行业参与者的支持。它有望成为连接此类硬件的事实标准。

UALink 1.0 规范为加速器定义了高速、低延迟的互连,支持每通道 200 GT/s 的最大双向数据速率,信号速率为 212.5 GT/s,以适应前向纠错和编码开销。UALink 可以配置为 x1、x2 或 x4,四通道链路在发射和接收方向上都能实现高达 800 GT/s。

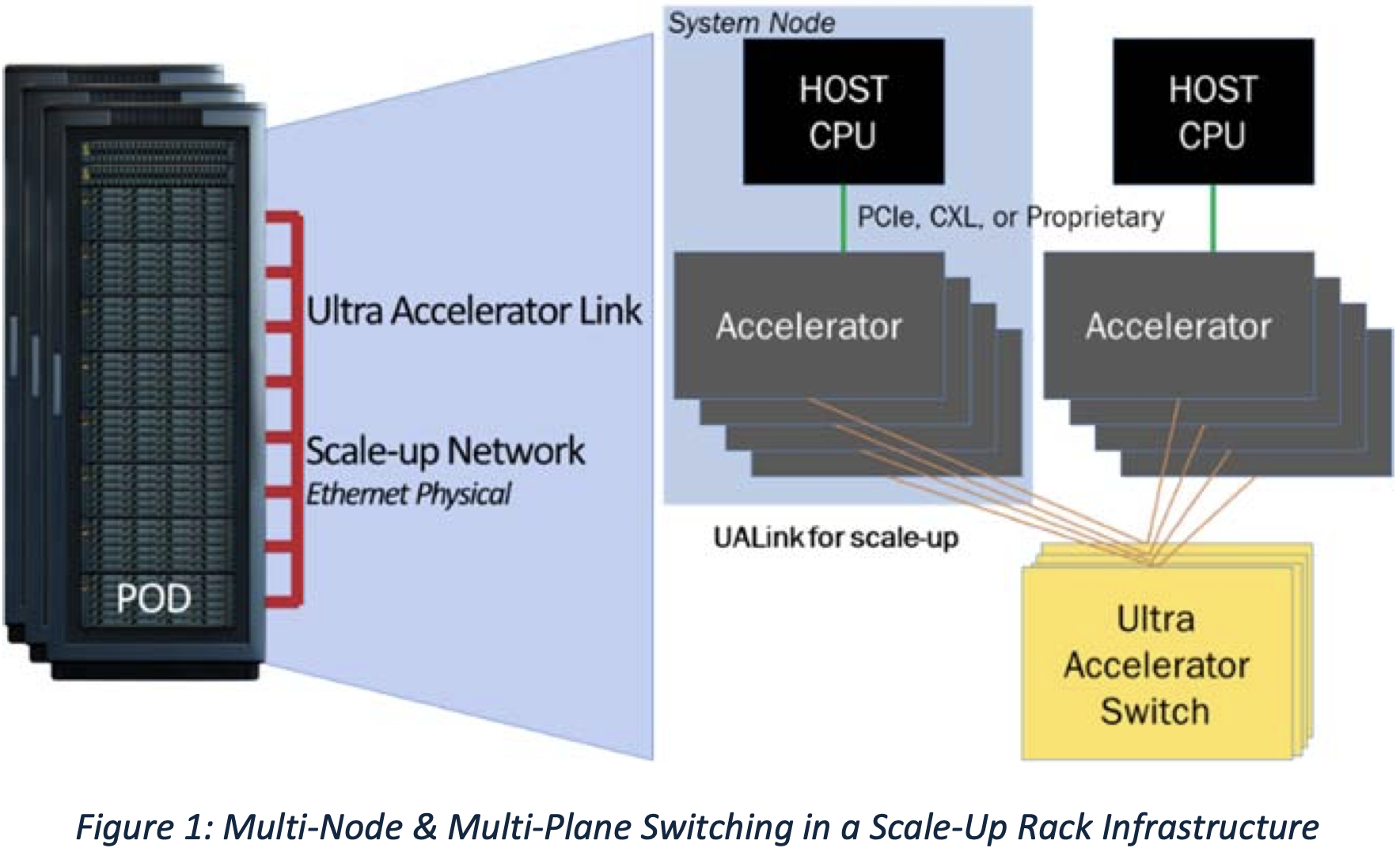

一个 UALink 系统支持多达 1,024 个加速器(GPU 或其他),通过 UALink 交换机连接,每个加速器分配一个端口和一个 10 位唯一标识符,以实现精确路由。UALink 电缆长度针对 <4 米进行了优化,可在 64B/640B 有效载荷下实现 <1 μs 的往返延迟。这些链路支持跨 1 到 4 个机架的确定性性能。

(图片来源:UALink)

UALink 协议栈包括四个硬件优化层:物理层、数据链路层、事务层和协议层。物理层使用标准以太网组件(例如 200GBASE-KR1/CR1),并包括使用 FEC 减少延迟的修改。数据链路层将来自事务层的 64 字节 fit 打包成 640 字节的单元,应用 CRC 和可选的重试逻辑。此层还处理设备间消息传递,并支持 UART 样式的固件通信。

事务层实现压缩寻址,在实际工作负载下以高达 95% 的协议效率简化数据传输。它还支持直接内存作,例如加速器之间的读取、写入和原子事务,从而保持本地和远程内存空间的顺序。

由于 UALink 协议针对现代数据中心,因此支持集成的安全和管理功能。例如,UALinkSec 为所有流量提供硬件级加密和身份验证,防止物理篡改,并通过租户控制的可信执行环境(如 AMD SEV、Arm CCA 和 Intel TDX)支持机密计算。该规范允许虚拟 Pod 分区,其中加速器组通过交换机级配置在单个 Pod 中隔离,以在共享基础设施上启用并发多租户工作负载。

UALink Pods 将通过专用控制软件和固件代理使用 PCIe 和以太网等标准接口进行管理。通过 REST API、遥测、工作负载控制和故障隔离支持完全可管理性。

UALink 联盟主席 Peter Onufryk 表示:“随着 UALink 200G 1.0 规范的发布,UALink 联盟的成员公司正在积极构建一个用于纵向扩展加速器连接的开放生态系统。我们很高兴见证即将进入市场并支持未来 AI 应用的各种解决方案。

Nvidia 目前在 AI 加速器市场占据主导地位,这要归功于其强大的生态系统和纵向扩展解决方案。它目前正在发货 Blackwell NVL72 机架,这些机架使用 NVLink 在单个机架中连接多达 72 个 GPU,机架间 Pod 允许在单个 Pod 中连接多达 576 个 Blackwell B200 GPU。随着明年即将推出的 Vera Rubin 平台,Nvidia 打算在单个机架中扩展到 144 个 GPU,而 Rubin Ultra 将在 2027 年扩展到单个机架中高达 576 个 GPU。

评论