继续缩小or改变封装 谁是芯片未来的“康庄大道”?

随着在单个die上集成各式各样的功能模块(部件)的成本持续上升,先进封装正迅速成为芯片制造商的主流选择。

尽管围绕这一转变已经有好几年的讨论,但实际情况是,它经历了半个多世纪才得以实现。上世纪60年代,先进封装始于IBM的倒装芯片,而在20世纪90年代,随着多芯片模组的出现,先进封装技术又得到了进一步提升,特别是在mil/aero市场。尽管如此,先进封装此前从未成为商业芯片制造商的首选,因为在硅领域,缩小特征尺寸的成本更低,针对等比例缩小的工具和IP生态系统已经很好地建立起来,并且从设计到盈利的时间(time-to-profitability)也更明确。

随着finFETs和double patterning的引入,16/14nm节点处的经济发生显著变化。在更新的节点上,设计和制造成本将不断增加。特征尺寸的缩小在5nm节点的过孔甚至和互连将需要新材料,5nm或3nm节点上需要新型晶体管结构(目前来看,最可能的是全栅FET)。此外需要高数值孔径的EUV,以及新的刻蚀、沉积和检测设备。总而言之,这些步骤增加了在先进工艺流程中开发和制造芯片的成本,能够用足够的体量来对冲这剧增成本的市场机会变得越来越少。

尽管EUV技术的持续延迟迫使设计团队采用metal1和metal2的多重曝光,但上述的那些因素对于半导体行业来说并不意外。然而,行业需要时间来开发可行的替代方案,并证明和改进方案。EDA供应商正在提供设计工具和完整的流程,支持选择各种封装技术构建芯片,并且在高可见性市场(高知名度市场)中生产足够的先进封装芯片,以证明该方案是可行的,比如苹果、AMD、华为、思科、IBM和赛灵思(Xilinx)等供应商,以及3D NAND、高带宽内存(HBM)和混合内存立方体(Hybrid Memory Cube)等技术。

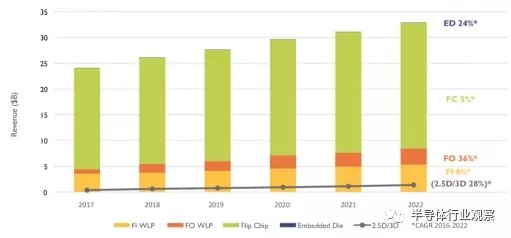

另外,在全球最大的IDM公司中,英特尔和三星现已提供低成本的专有桥接技术及代工服务。除了2.5D和3D封装技术之外,所有主要的OSAT都提供一个或多个版本的扇出型晶圆级封装(fan-out wafer-level packaging,fan-out WLP)技术。先进封装各个领域的增长反映了这一现状。

图 1:不同平台的先进封装营收(纵坐标单位为十亿美元)。资料来源:Yole Developpement研究机构于2017年5月发布的2017年先进封装行业报告

自动化工具的设计

先进封装市场增长的迹象之一是设计自动化工具的发展。在三大EDA供应商中,Cadence是率先提供封装工具和解决方案。早在上个世纪九十年代,Cadence就进入了这一市场,自2000年以来,它一直基于模拟芯片设计并不能简单套用等比例缩小原理的事实而从事相关的工具开发。而这一远见花了近15年的时间,终于成为市场主流,其他EDA供应商也发现了封装领域是一个值得投入研发的机会。

本月初,被西门子收购的Mentor推出了用于先进封装的流程和新工具。该公司的高级IC封装解决方案部门——Board Systems Division的产品营销经理Keith Felton说:“这个工艺现在类似于硅工艺。我们预计将推出多个设计套件。因此,您将看到两个用于fan-out晶圆级封装的套件,每个封装都有细微变化,同时还将推出堆叠die,基板上晶圆上芯片(chip on wafer on substrate,CoWoS),高引脚数倒装芯片和系统级芯片封装(system-in-package,SiP)等多种封装技术”。

Felton表示,上述设计套件将与其他工具一起使用,包括DFMtools和PCB分析和验证工具。

ANSYS总经理兼副总裁John Lee表示:“这些都是基于物理的仿真。这不仅仅是关于半导体的问题,还是热分析和机械模拟。以台积电的InFO技术硅片的晶圆级封装为例,由于明显的物理效应,需要进行同步热学分析。这可能发生在7nm、10nm、16nm甚至更早的工艺节点。但散发热量的元件将影响系统的可靠性。所以如果你考虑的是电迁移而不是热效应,那你的分析可能会偏悲观;然而如果所以,如果你谈论的是电迁移而不是热量,那么你可能对世界有一个悲观的看法。如果你的观点不是悲观的,那将会很危险的”。

Synopsys公司董事长兼联合首席执行官Aart de Geus表示,真正的关键在于将整个系统可视化,并构建跨封装方案的组件和工具。“因此,在IP解决方案上,你必须对其进行描述使之在任何情况下都有效。整体仿真是对由各种形式的多个芯片组成的系统进行仿真,当然也包括软件仿真。对设计人员来说,建立模型和原型的能力至关重要。包括针对数字和混合信号相关的设计”。

de Geus指出,它(代指上面的系统可视化?跨封装方案的组件和工具?整体仿真?还是建立模型?我没找到相关资料,前后文又联系不起来,没法准确翻译)该解决方案还包括硬件模拟(emulation)和软件原型,“不管是在封装内部还是在7nm SoC上,你需要能够在这些虚拟的硬件上运行软件”。

但这些应用于先进封装的工具,在预测的准确性上都还有很长一段路需要继续探索。

“EDA设计工具将给半导体行业带来巨大影响,”TechSearch International总裁Jan Vardaman表示:“如果没有设计工具,很多事情都无法完成,未来工具应用将更加广泛。在一个设计中,只要划分允许,你想尽可能多地使用成熟工艺,为此,我们迫切需要设计工具。”

评论