7纳米以下技术候选人:IMEC看好GAA NWFET技术

比利时微电子(IMEC)在2016国际电子元件会议(IEEE International Electron Devices Meeting ; IEDM)中首度提出由硅纳米线垂直堆叠的环绕式闸极(GAA)金属氧化物半导体场效电晶体(MOSFETs)的CMOS集成电路,其关键技术在于双功率金属闸极,使得n型和p型装置的临界电压得以相等,且针对7纳米以下技术候选人,IMEC看好环绕式闸极纳米线电晶体(GAA NWFET)会雀屏中选。

本文引用地址:https://www.eepw.com.cn/article/201612/341419.htm比利时微电子研究中心与全球许多半导体大厂、系统大厂均为先进制程和创新技术的合作伙伴;其中,在CMOS先进逻辑微缩技术研究的关键伙伴包括有台积电、三星电子(Samsung Electronics)、高通(Qualcomm)、GlobalFoundries、美光(Micron)、英特尔(Intel)、SK海力士(SK Hynix)、Sony、华为等。

针对半导体7纳米以下制程,究竟谁可以接棒FinFET技术?比利时微电子研究中心表示,目前看起来环绕式闸极纳米线电晶体(GAA NWFET)是最有可能成功突破7纳米以下FinFET制程的候选人。

比利时微电子进一步分析,因为GAA NWFET拥有高静电掌控能力,可以实现CMOS微缩,在水平配置中,也是目前主流FinFET技术的自然延伸,可以通过垂直堆叠多条水平纳米线来最大化每个覆盖区的驱动电流。

再者,比利时微电子研究中心也研究新的结构对于原来静电放电(ESD)表现的影响,且发表静电放电防护二极体,让GAA纳米MOSFETs的发展有突破,间接帮助鳍式场效电晶体(FinFET)持续往更先进制程技术发展。

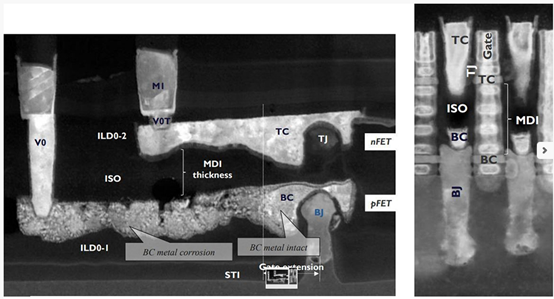

2016年比利时微电子研究中心展示了垂直堆叠、由直径8纳米的硅纳米线所制成的GAA FET,这些电晶体的静电控制由n-FETs和p-FETs制作而成,具有n型和p型元件的相同临界电压,因为积体电路技术中的关键是双功函数金属闸极的使用,使得n-FET和p-FET的临界电压得以独立设置。

且在该步骤中,P型功函数金属(PWFM)在所有元件中的沟槽式闸极使用,然后使用选择性蚀刻P型功函数金属到纳米结晶性铪氧化物(HfO2)到n-FET,随后利用N型功函数金属。

另外,针对关键静电放电(ESD)影响,比利时微电子提出两种不同的静电放电防护二极管,分别为闸二极体和浅沟槽隔离(STI)二极体。其中,STI二极体因为在二次崩溃电流(It2)与寄生电容的比率上表现较佳,所以认为是较好的静电放电防护元件。

再者,测量和TCAD模拟也证明,与块状基板式鳍式电晶体(Bulk FinFET)二极体相比,GAA纳米线二极体维持了静电放电的表现。

比利时微电子研究中心的逻辑装置与积体电路总监Dan Mocuta表示,在GAA硅质CMOS技术、静电放电防护结果方面的积体电路技术,是实现7纳米或以下制程的重要成就。

评论