基于半导体存储芯片K9WBG08U1M的大容量存储器

O 引言

本文引用地址:https://www.eepw.com.cn/article/151331.htm随着航空航天航海等技术的发展,无论是星载还是舰载方面的技术要求,都迫切希望有一种能够在恶劣环境(高温、低温、振动)下正常工作,并且易于保存的大容量视频记录设备,以满足数据管理系统方面的要求。

早期的海量数据记录主要是使用磁带机,但存放在磁带机中的数据保存条件较高,它容易受到天气和湿度等环境的影响。而使用半导体存储芯片作为存储介质则具有存储密度高、无转动部件、可靠性高、体积小、重量轻等特点,因此,半导体存储芯片逐渐成为高可靠性数据记录器的主流方案。

基于半导体存储芯片K9WBG08U1M的大容量存储器,可以很好的满足工业控制或军事领域等恶劣环境下的使用要求。

1.1 系统组成

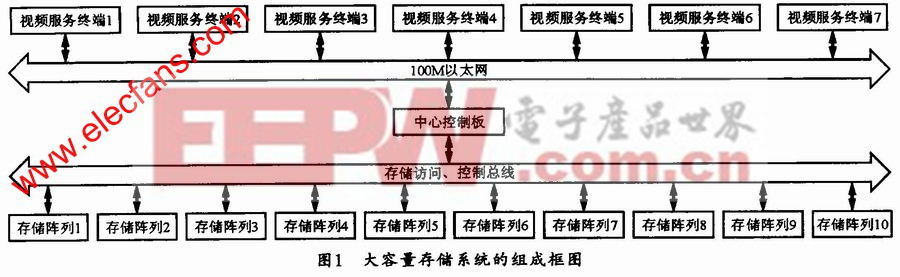

整个视频压缩与大容量数据存储系统一般由多路视频服务终端、中心控制分系统、大容量电子存储阵列等组成。其中,多路视频服务终端用于视频信号的采集和压缩,压缩后的视频数据通过网络送入存储阵列保存,也可以通过以太网送到指定的用户进行浏览;中心控制分系统以高性能嵌入式处理器BF537为核心,可完成视频服务终端的控制,存储阵列数据的读出。它通过百兆以太网与上位机进行高速数据交换;存储阵列可提供高达4T的存储深度,它由10块400MByte容量的独立存储板组成,可为多路视频服务终端提供同时存储服务,存储介质采用大容量非易失NAND-Flash芯片K9WBG08U1M,单片存储容量为32Gbit,每块存储板都可由视频服务终端写入,并由中心控制分系统读出。其系统组成框图如图1所示。

1.2 系统工作原理

摄像机输出的视频信号进入视频采集压缩卡后,首先通过A/D变换器进行视频信号采集,采样后输出的数字视频信号经FPGA整理后进入数字信号处理器DSP,然后对视频数据在DSP中按照MPEG4协议进行视频压缩,形成MPEG4格式的视频数据流;每块采集压缩板的视频数据流可实时保存到存储阵列中。如果有用户需要访问,则将该数据流打包后发送给指定的用户。

压缩和存储过程受主控计算机的控制。如果有用户需要浏览保存的视频数据,则需要向主控计算机发出浏览请求,主控计算机接受后,即可通过读数据逻辑选择存储阵列中的数据块,然后读出后打包并发送给指定的用户。主控计算机可以同时响应多个用户的请求。

2 大容量电子存储阵列设计

2.1 数据收发接口

存储板的数据收发可通过DSP实现。考虑到与前端芯片选择的一致性,本方案选择ADI公司的ADSP-BF533为数据收发处理器。执行存储操作时,BF533将从输入/输出总线并行外设接口(PPI)接收中心控制板发送的存储数据,并将其缓存到SDRAM,同时按照K9WBG08U1M的编程时序要求形成存储器的编程指令,再通过FPGA发送到K9WBG08U1M存储芯片;而在执行读操作时,BF533则通过FPGA向K9WBG08U1M发送读操作指令,以读取指定区域的数据并缓存到SDRAM存储器中,然后通过输入/输出总线(PPI)发送到中心控制分系统并将其回送给上位机进行浏览。

评论