采用CPLD的MAX1032采样控制的实现方法

0 引言

本文主要介绍MAX1032采样芯片以及使用CPLD对MAX1032采样进行控制的方法。事实上,虽然微控制器也能对MAX1032进行方便的控制,但使用CPLD来控制系统外围设备,可以节省微控制器的资源,减轻其负担,同时可以让其处理更复杂的信息,而利用CPLD对时序进行控制则

更精确。

1 MAX1032的主要功能

MAX1032是美信公司推出的AD采样芯片MAX1030-MAX1033系列中一款。该系列是采样范围可达±12 V的多量程、低功耗、14位逐次逼近型串行输出模数转换器(ADC),数据传输符合SPI协议。当采用+5 V单电源供电时,其转换速率高达115 ksps。

MAX1032内部主要由模拟输入复用器及多通道电路、控制逻辑和寄存器、可编程增益放大器(PGA)逐次逼近数模转换器(SAR ADC)、串行I/O(Serial I/O)以及先进先出寄存器(FIFO)等主要模块构成。

MAX1032的各引脚功能如下:

CH0~CH7:模拟信号输入端。单端输入范围为:O~+6 V、-6 V~0、0~+12 V、-12 V~0和±3V;

±6 V,±12 V,差分输入,范围为:±6 V、±12V和±24V;

![]() :片选输入,低电平有效。只有该端置低,数据才可同步输入(DIN)或输出(DOUT);

:片选输入,低电平有效。只有该端置低,数据才可同步输入(DIN)或输出(DOUT);

DIN:串行数据输入。![]() 为低时,DIN上的数据在SCLK的上升沿输入片内;

为低时,DIN上的数据在SCLK的上升沿输入片内;

SSTRB:串行触发输出。在内部时钟模式下,SSTRB的上升沿跳变表明转换完成;在外部时钟模式下,SSTRB一直为低电平;

SCLK:串行时钟输入;

DOUT:串行数据输出。在![]() 为低时,DOUT上的数据在SCLK的下降沿输出;

为低时,DOUT上的数据在SCLK的下降沿输出;![]() 置高时,DOUT为高阻状态;

置高时,DOUT为高阻状态;

REFCAP:参考电压旁路端。对于外部参考电压模式。REFCAP连到AVDD;对于内部参考电压模式,通过一个0.01μf的电容连到AGNDl;

REF:内部基准电压输出或外部基准电压输入。在外部参考电压模式下,REF端可接由外部电路提供的3.800-4.0136 V的基准电压;在内部参考电压模式下。REF端与AGNDl端之间必须连接容量为1μF的滤波电容,该端由芯片内部提供4.096 V参考电压:

DGNDO:数字I/O地;

DGND:数字地;

DVDDO:数字I/O电源输入。输入范围为+2.7~+5.25 V:

DVDD:数字电源输入;

AVDDl:模拟输入电源1,输入范围为+4.75~+5.25 V:

AVDD2:模拟输入电源2,输入范围为+4.75~+5.25 V:

AGNDl:模拟地1;

AGND2:模拟地2;

AGND3:模拟地3。

设计时,AGNDl,AGND2,AGND3,DGNDO,DGND必须接到一起。

2 MAX1032的工作原理

在使用MAX1032进行采样前,通常需要确认信号的输入阻抗在17 kΩ以内。

MAX1032总共有三种工作模式:外部时钟模式,外部采样模式和内部时钟模式。本文将针对。MAX1032的外部时钟模式并结合CPLD给出实际的应用方案。

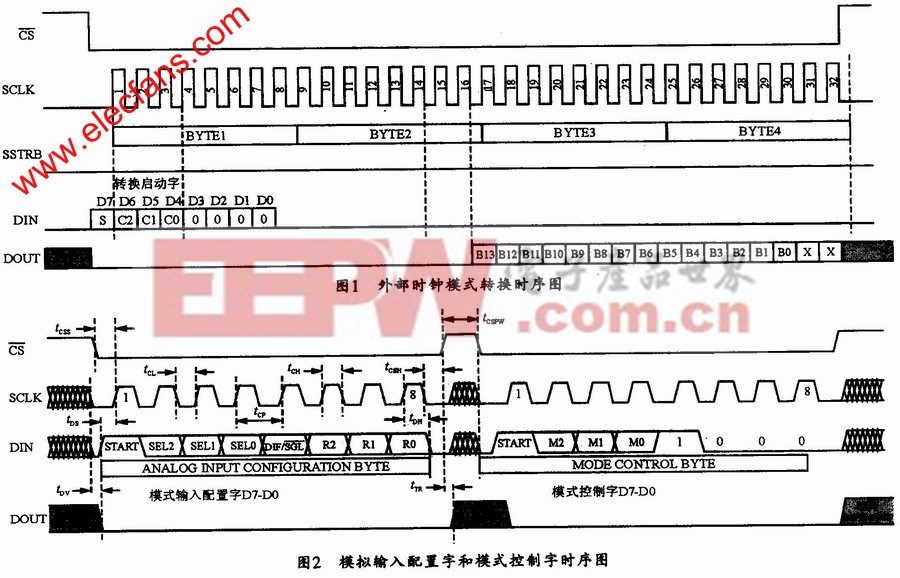

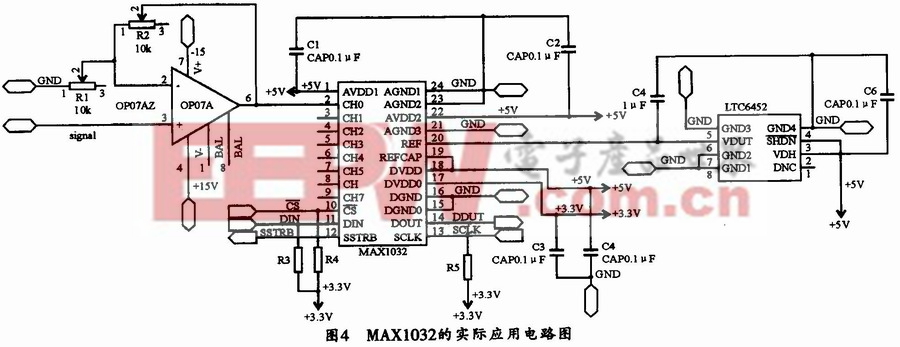

外部时钟模式:以最快的转换速率达到最大的吞吐量,由用户直接控制采样时,CSn在转换过程中始终为低,这时,用户可通过SCLK控制A/D的转换并对结果读取。SSTRB始终为低,其转换时序图如图1所示。SCLK的周期(tCP)必须在272 ns~62 us之间。其中高低电平宽度均需大于109 ns(tCL,tCH)。在CSn由高变低后的40 ns(tCSS),可以开始对SCLK上跳沿计数,DIN的输入建立时间至少40 ns (tDS),DIN将在SCLK上跳沿时同步输入(tDH),SCLK上跳沿之后,将忽略DIN。在CSn变低之后40 ns(tDV)内,DOUT开始有效,而在CSn拉高后40 ns(tTR)内,DOUT将输出保持高阻态,其时序描述如图2所示。

在内部时钟模式,系统将以较快的速率达到最大的吞吐量,并由内部时钟控制采样,用户只需提供一个字节的SCLK,再拉高CSn,即可启动转换。和外部采样模式相同,SSTRB上跳变表示转换完成,此时,用户便可提供两个字节的SCLK来读取转换结果。

在外部采样模式,系统将以最慢的转换速率达到最大的吞吐量,并由用户直接控制采样,用户可提供两个字节的SCLK,再将CSn拉高,以启动转换。SSTRB上跳变表示转换完成,用户提供两个字节的SCLK可读取转换结果。

MAX1032总共有三个控制字:模拟输入配置字、模式控制字和转换启动字。图2所示是模拟输入控制字和模式控制字的工作时序图。三个控制字均为8位。

对于模拟输入配置字,DO~D2是选择量程的,MAX1032总共有10种量程可以选择;D3是差分/单端选择位,为低表示采样信号为单端输入.为高表示差分输入。D4~D6是输入通道选择,总共有8个采样通道。D7是字开始位,置高表示字输入开始。

对于模式控制字,D0~D2必须为低,D3必须为高。D4~D6用于工作状态选择,总共有6种工作状态。D7是字开始位,同样,置高表示字输入启动。

转换启动字D7是字开始位,D4~D2是输入通道选择。用法和模拟输入配置字相同,操作时DO~D3必须为低。

三个控制字的输入顺序是模拟输入配置字,模式控制字,转换启动字。

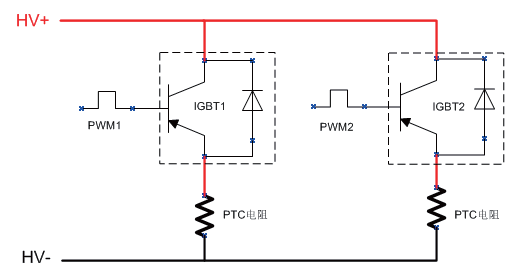

3 硬件设计

图3所示是本系统的结构框图。由图3可见,模拟采样信号先经过一个运放。运放的作用是降低输入阻抗。以达到MAX1032输入阻抗小于17kΩ的要求。之后,再将利用CPLD控制MAX1032进行采样,采样结果回送至CPLD,之后经过处理后的数据传到系统,由系统再将一系列二进制数换算成最终的结果。框图里的系统可以是嵌入式微控制器,也可以是数字输入输出卡等控制系统。

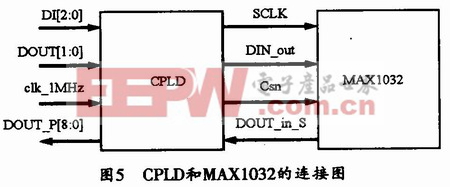

图4所示是MAX1032的应用电路图。由于MAX1032只允许输入阻抗小于17 kΩ,而有的采样信号不一定能满足这一要求,故需要对采样信

号进行一定处理,以降低信号的输出阻抗。由于射极跟随器的输出阻抗趋于零,故将待采样信号连到射极跟随器上可以有效降低其输出阻抗。本文选用的运放为OP07,该运放具有很低的输入失调电压和漂移,而且精度相当高,适合作为模拟信号前置运放。如将OP07接成负反馈模式,使输出等于1+R1/R2,并将滑动变阻器R1调至0Ω,那么它就可以当做电压跟随器使用。

图4中,MAX1032的外部参考电压由LTC6652提供。LTC6652是高精度电位参考芯片,本文使用4.096 V作为MAX1032外部参考电压。REFCAP在此模式下可接到5 V电源。由于MAX1032是由CPLD控制,故将DVDDO连到3.3 V。

4 CPLD逻辑设计

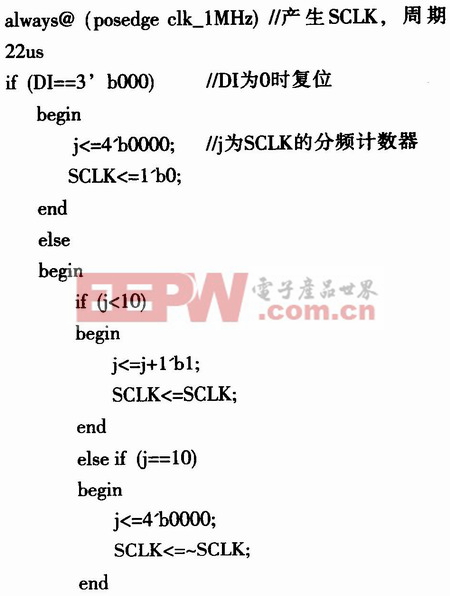

CPLD和MAX1032的连接图如图5所示。其中,CPLD可以选用Ahera公司的MAXII系列器件EPM240或EPM570。

CPID的程序设计主要由两部分组成,第一部分是产生MAX1032的控制信号,第二部分是对MAX1032的输出结果进行处理。

clk_1MHZ为CPLD时钟,选1 MHz。通过CPLD可在内部对时钟进行分频,输出SCLK可作为MAX1032的输入时钟。DI由系统给CPLD输入,作用是选择MAX1032的控制字,同时也是CPLD的复位控制。DIN_out是给MAX1032加载的串行控制字,其加载时序可利用计数器控制。本例采用外部时钟模式,模拟输入配置字为10000110。第七位1是字开始标志;六到四位为0表示选择CH0通道输入,第三位为0表示采样信号单端输入;二到零位为110,表示量程选择0~12 V。模式控制字为10001000,第七位1是字开始标志,六到四位为0表示使用外部时钟模式。三到零位为100 0是芯片强制输入。加载完模拟输入配置字和模式控制字之后,就可以启动采样,以加载转换启动字开始采样。转换启动字为10000000时,第七位1是字开始标志,六到四位为0表示选择CH0通道输入,三到零位为0000是芯片强制输入。MAX1032控制协议和SPI类似,在SCLK的上跳沿输入,下跳沿输出。片选信号CSn时序利用计数器控制,每个控制字之间的CSn必须有一个高脉冲,脉宽至少40 ns(tCSPW),每个控制字输入完后,CSn可以立即拉高(tCSH)。以下是可综合的MAX1032控制程序的主要代码:

评论