imec采用High-NA EUV技术 展示逻辑与DRAM架构

比利时微电子研究中心(imec),在荷兰费尔德霍温与艾司摩尔(ASML)合作建立的高数值孔径极紫外光(high-NA EUV)微影实验室中,利用数值孔径0.55的极紫外光曝光机,发表了曝光后的图形化组件结构。在单次曝光后,9纳米和5纳米(间距19纳米)的随机逻辑结构、中心间距为30纳米的随机通孔、间距为22纳米的二维特征,以及间距为32纳米的动态随机存取内存(DRAM)专用布局全部成功成形,采用的是由imec与其先进图形化研究计划伙伴所优化的材料和基线制程。透过这些研究成果,imec证实该微影技术的生态系统已经准备就绪,能够实现高分辨率的high NA EUV单次曝光。

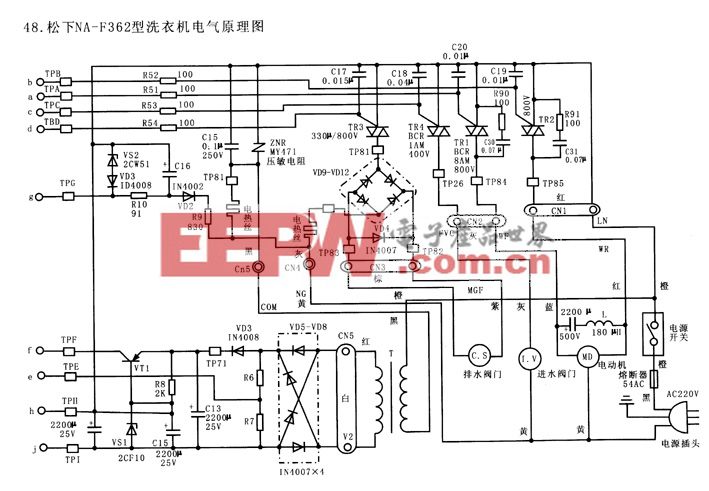

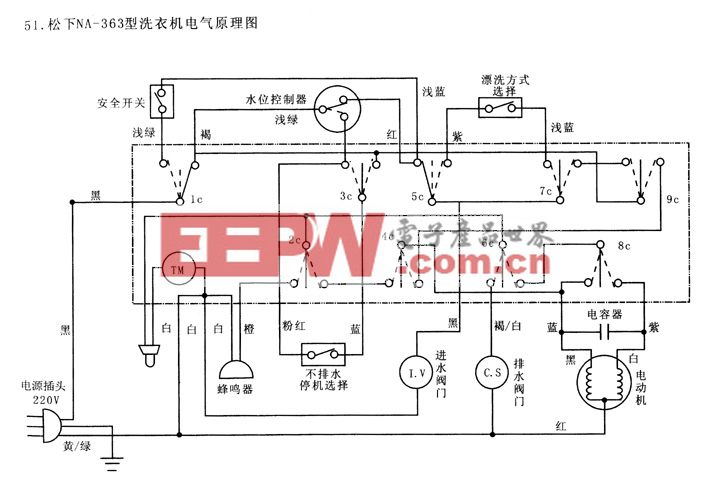

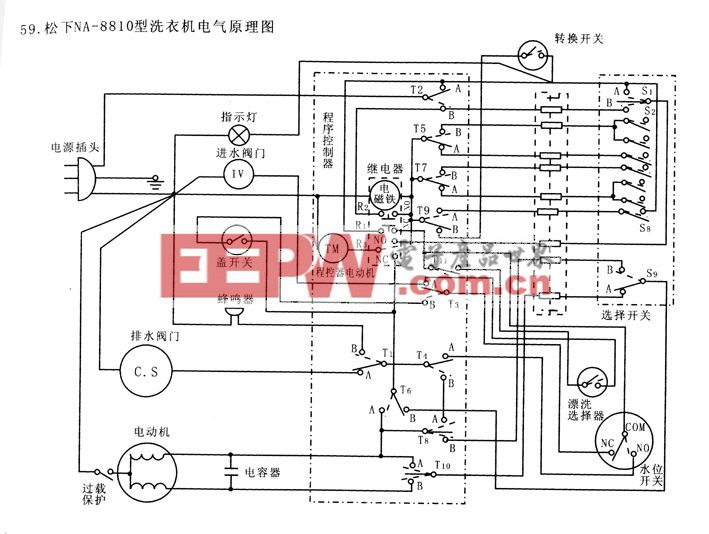

(a)imec为DRAM应用展示电荷储存节点连接垫与位线周边电路的整合;(b)图形转移后的9纳米及5纳米随机逻辑结构(间距为19纳米)。

由艾司摩尔与imec共同成立于荷兰费尔德霍温的High NA EUV微影实验室在近期启用后,客户现在可以使用TWINSCAN EXE:5000高数值孔径极紫外光曝光机来开发非公开的high NA EUV应用案例,这些案例也能运用客户各自的设计规则和布局。

imec成功利用单次曝光,形成间隔为9纳米与半线宽为5纳米的随机逻辑结构,相当于间距为19纳米,图形顶端(tip-to-tip)的间距达到20纳米以下。中心间距为30纳米的随机通孔充分展示了绝佳的图形保真度与关键尺寸均匀度。此外,间距为22纳米的二维特征也展现了杰出的性能,突显了利用高数值孔径微影技术来实现2D布线的发展潜力。

除了逻辑结构,imec也成功利用单次曝光,为动态随机存取内存(DRAM)制出把电荷储存节点连接垫(storage node landing pad)与周边位线相互整合的组件图形。这项成就彰显了高数值孔径技术的潜能,可望透过单次曝光来取代多层光罩的曝光需求。

取得这些突破性成果后,imec携手艾司摩尔—与其伙伴紧密合作,开始紧锣密鼓地进行准备工作,为第一代High NA EUV微影技术来筹备图形化生态系统与量测技术。在进行多次曝光之前,imec准备了专用的晶圆堆栈(包含先进光阻、涂布底层及光罩),并把像是光学临近校正(OPC)、整合图形化及蚀刻技术等high NA EUV基线制程整合到0.55NA EUV曝光机台上。

imec运算技术及系统/运算系统微缩研究计划的资深副总裁(SVP)Steven Scheer表示:「我们很高兴能在艾司摩尔与imec共同建立的实验室展示全球首次利用high NA技术完成的逻辑及内存组件图形化,这也是业界应用的首次认证。结果显示,在利用单次曝光成像来积极微缩2D特征图形的方面,High NA EUV技术展现了独特的潜能,不仅改善了设计弹性,也减少了图形化的成本与复杂度。面向未来,我们期待能够提供价值洞见给图形化生态系统的合作伙伴,协助他们进一步推动High NA EUV专用材料及设备的发展。」

imec执行长Luc Van den hov表示:「此次成果证实了高数值孔径EUV技术具备长远预测的分辨率能力,目标是利用单次曝光来制出间距为20纳米以下的金属层。因此,High NA EUV技术将会为延续逻辑和内存技术的尺寸微缩提供莫大的帮助,这也是推进组件发展蓝图迈向埃米世代的一大重要支柱。这些早期技术展示全都是因为艾司摩尔与imec共同实验室的成立才得以实现,该实验室能让我们的合作伙伴加速把高数值孔径微影技术引进量产。」

评论