Intel宣布一项技术突破 内存加工工艺可缩小到5纳米

英特尔和芯片技术公司Numonyx本周三发布了一项新技术.这两家公司称,这种新技术将使非易失性存储器突破NAND闪存的20纳米的极限,使加工工艺缩小到5纳米,从而更加节省成本.

本文引用地址:https://www.eepw.com.cn/article/99391.htm英特尔研究员和内存技术开发经理Al Fazio星期三向记者解释说,这种技术产生的堆叠内存阵列有可能取代目前DRAM内存和NAND闪存的一些工作.这种技术甚至能够让系统设计师把一些DRAM内存和固态内存的一些存储属性缩小到一个内存类.

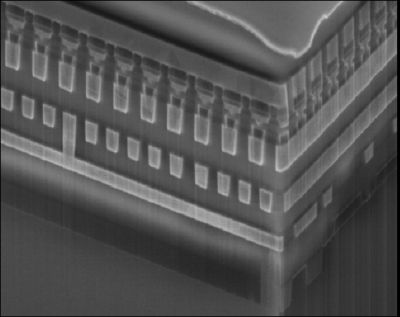

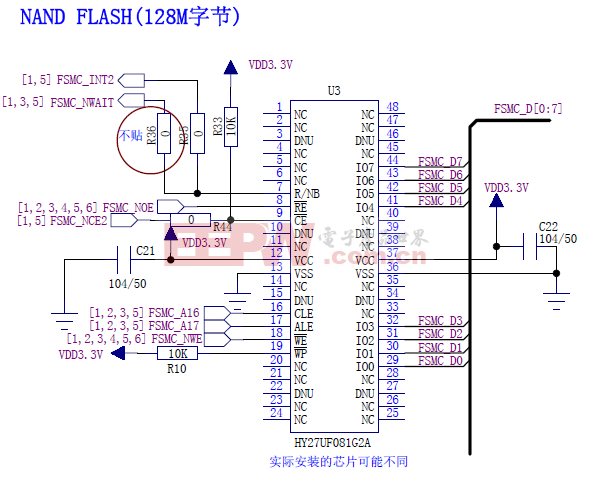

This image shows phase-change memory built atop a conventional CMOS microchip. Memory cells can be controlled using rows and columns of wires that lead through the chip.

(Credit: Intel)

简单地说,这个技术能够使DRAM内存和存储结合为一个高速的、高带宽的架构.但是,这个飞跃还有很长的路要走.基于本周三宣布的这种技术的产品还要等许多年才能出现.

Fazio和Numonyx公司高级技术研究员Greg Atwood解释的这项技术突破称作PCMS(相变内存与开关)的相变内存(PCM)技术的一个进步.这种技术能够在同一个基本的硫族(元素)化物材料商创建薄膜内存单元机器控制薄膜选择器,并且在一个交叉点架构上把这些元件组合在一起.

这种新的相变技术也许有一天会把你的内存和存储融合为一个幸福的家庭.

这种新的薄膜选择器名为双向阈值开关,允许把多层的内存/选择器层放在一个CMOS基础上,以创建高密度、高带宽的PCM内存.

这种多层堆叠是这个目标.本周三宣布的技术突破是一种可工作的64MB单层版本的这种新的内存架构.英特尔将在今年12月在马里兰州巴尔迪摩举行的国际电子设备大会上发表一篇论文,正式介绍这种内存架构.

不过,这些多层的新内存目前正在设计图版上.正如Atwood说的那样,第一次是难度最大的一层.

评论