一种系统芯片的功能测试方法

1 引言

一个正确的电路设计拿到工厂去制造,并不可能百分之百的正确地制造出来。总会受到种种不确定性的影响,比如制造机器的偏差、环境干扰、硅片的质量不一致甚至是一些人为的失误等等方面的影响,生产出的产品并不全都是完好的。如果芯片存在有故障,这样的芯片是绝对不允许流入市场中的。那么如何检验出有制造缺陷的芯片,这就属于测试的范畴。在深亚微米阶段,线宽非常精细,工序数量又多,更加容易受到干扰的影响,制造故障变得尤其明显。所以必须加大测试的力度,尽可能地减少次品流人市场的几率。

下面将通过设计一个系统芯片——“成电之芯”的功能测试平台来具体介绍实现系统芯片功能测试的方法。

2 评估测试需求

在进行功能测试和选用必要的工具之前,应该审定系统芯片测试的基本要求,并明确解决如下4个问题闭:1)哪些是必须的基本测试能力;2)怎样观察对测试序列的响应;3)测试平台需要多高的灵活性;4)需要多少经费和时间。

对基本测试平台能力[3]的评估应该包括:1)所需的激励时钟速度;2)所需的激励通道数;3)输入的电压标准;4)测试序列的长度。

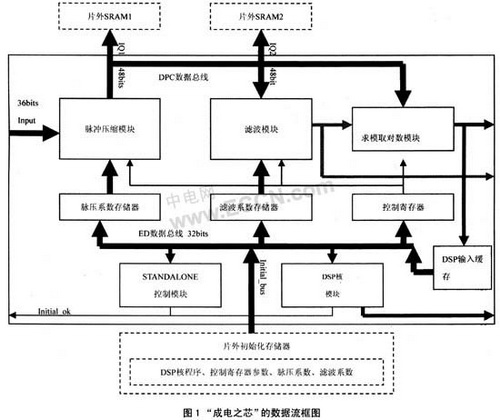

“成电之芯”是一款0.18μm工艺、内嵌DSP核的730万门SoC,面积31mm×31mm,PBGA609封装,它的硬件部分主要实现脉冲压缩、动目标显示(MTI)、动目标检测(MTD)、求模取对数等算法,其中脉冲压缩比最大可做到1024,MTD滤波通道数最大为256,每个通道的滤波器阶数最大为256,每个相参处理间隔的数据量最大为2M深度,MTI滤波最多可做16脉冲对消,根据雷达整机系统需求,上述参数可灵活调节,通过DSP核,可用软件实现其它各类数字信号处理算法(如CFAR等)。芯片的内部处理速度最快160MHz,外部I/O速率范围为1~80MHz。芯片I/O电平为LVTTI电平。该芯片的数据流框图如图1所示。

图1中,实线区域为芯片内部各模块,虚线部分为片外存储器。从图中可以看出,雷达信号处理专用芯片的数据传输主要由DPC数据总线和ED数据总线完成。

通过上述对“成电之芯”的简单介绍,该芯片的系统功能和测试平台的能力需求已经一目了然。

3 功能测试平台的建立

3.1 功能测试平台建立方法

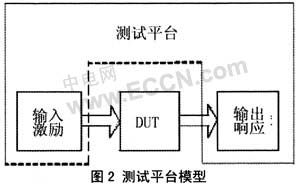

测试平台是为了向被测芯片施加输入激励而建立起来的。如图2所示,测试平台向被测芯片输入激励,对输出采样,并将结果与期望值比较,得出比较分析结果。

建立测试平台的过程是建立在对被测芯片功能属性透彻理解的基础上的。目前,常用的测试平台建立方法有:采用可编程器件建立测试平台、基于波形建立测试平台、基于可编程测试仪建立测试平台和基于事物建立平台。

评论