imec首度展示晶背供电逻辑IC布线方案 推动2D/3D IC升级

比利时微电子研究中心(imec)于本周举行的2022年IEEE国际超大规模集成电路技术研讨会(VLSI Symposium),首度展示从晶背供电的逻辑IC布线方案,利用奈米硅穿孔(nTSV)结构,将晶圆正面的组件连接到埋入式电源轨(buried power rail)上。微缩化的鳍式场效晶体管(FinFET)透过这些埋入式电源轨(BPR)实现互连,性能不受晶背制程影响。

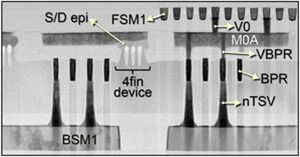

FinFET微缩组件透过奈米硅穿孔(nTSV)与埋入式电源轨(BPR)连接至晶圆背面,与晶圆正面连接则利用埋入式电源轨、通孔对电源轨(via to BPR;VBPR)以及电源超出主动区(metal over active;MOA)的结构设计。

这套先进的布线方案能分离电源线与讯号线的配置,推动2nm以下逻辑芯片持续微缩,还能增强供电效能,进而提升系统性能。此外,imec也在晶圆背面导入了采用2.5D金属—绝缘体—金属(MIM)结构的电容,展现更佳的芯片效能。

晶背供电设计能分离逻辑IC的电源供应网络与讯号线,进而减缓后段制程布线壅塞的问题,还能带来优化供电效能的好处。2019年imec首次提出这项技术,不同的制程方案也随之出现。例如,在2021年VLSI技术研讨会,imec首度展示晶背导线互连的实例,将奈米硅穿孔连接到位于晶圆正面的M1金属层衬垫。

今年VLSI技术研讨会,imec在其发表的论文中展示一套进阶整合方案,透过埋入式电源轨,将FinFET微缩组件一齐连接到晶圆正面与背面,创下全球首例。imec的CMOS组件技术研究计划主持人Naoto Horiguchi表示:「我们相信,从微缩组件与提升性能的角度来看,采用晶背供电设计并导入埋入式电源轨是最有可能实现晶背供电网络的解决方案,这些电源轨在前段制程中埋入芯片,以局部布线的结构设计推动芯片微缩。」

他接着说明:「我们在开发测试芯片时,从晶圆正面定义埋入式电源轨的图形,随后将奈米硅穿孔连接到这些电源轨上,结果显示FinFET组件性能不受晶背制程影响,这就包含接合目标晶圆与承载晶圆、薄化晶背以及制造深度长达320nm的奈米硅穿孔。奈米硅穿孔以垂直向与埋入式电源轨紧密接合,各穿孔的间距仅200nm,不占用标准单元尺寸,能确保组件继续微缩至2nm以下。」

晶背供电设计可望从系统层面提升整体供电效能,尤其目前组件所需的功率密度持续攀升,供应电压或IR压降的问题也越来越严峻。imec的3D系统整合计划VP Eric Beyne表示:「我们在2022 VLSI技术研讨会上发表的一篇论文,在晶背制程中导入一颗2.5D柱状MIM结构的去耦电容。透过这颗2.5D电容,电容密度因此提升了4~5倍,IR压降现象与无电容(32.1%)及2D电容(23.5%)相比都来得低。这些分析结果来自一套经过实验数据校正的IR压降模拟架构。」

Eric Beyne总结:「我们的研究成果显示晶圆背面具备高弹性的设计空间,还能诉诸全新的设计选择,解决传统2D芯片微缩的痛点。此外,我们也展示了一些3D系统级微缩技术的效能,在剥离承载晶圆时,以功能性晶圆取而代之,例如用于3D SOC逻辑组件堆栈的逻辑晶圆,而底层的晶粒可从晶背取得电源供应。」

评论