FPGA芯片在高速数据采集缓存系统中的应用

摘要:给出了以FPGA为核心逻辑控制模块的高性能数据采集系统的设计方法,并在QuartusII8.0集成环境中进行软件设计和系统仿真,最后给出了新型缓存系统中主要功能模块的仿真图形。

关键词:FPGA;高速;数据采集;缓存

0 引言

在高速数据采集方面,FPGA有单片机和DSP无法比拟的优势。FPGA的时钟频率高.内部时延小,全部控制逻辑都可由硬件完成,而且速度

快,组成形式灵活,并可以集成外围控制、译码和接口电路。更最主要的是,FPGA可以采用IP内核技术,以通过继承、共享或购买所需的知识产权内核提高其开发进度。而利用EDA工具进行设计、综合和验证,则可加速设计过程,降低开发风险,缩短了开发周期。效率高而且更能适应市场。本数据采集系统就是基于FPGA技术设计的多路模拟量、数字量采集与处理系统。FPGA的10端口多,且可以自由编程、支配、定义其功能,同时配以verilogHDL语言以及芯片自带的可定制模块,即可进行软件设计。FPGA的最大优点是可在线编程。此外,基于FPGA设计的数据采集器还可以方便地进行远程功能扩展,以适应不同应用场合的需要。

1 系统基本构架

本文所设计的高速数据采集系统是某雷达信号处理系统的一部分,可用于雷达信号的预处理以及采集、缓存。本系统以高速FPCA为核心逻辑控制模块,并与高速ADC和DSP相连接。其系统基本架构如图1所示。

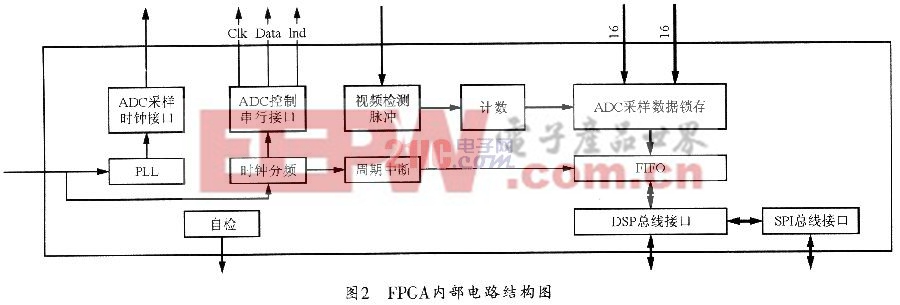

图l中的FPGA可用作数字接收机的预处理模块,该器件集成有PPL倍频、ADC控制接口、FIFO及其管理、SPI接口、DSP总线接口、状态和自

检模块等。FPGA的内部结构功能框图如图2所示。

图2中的中断产生模块用于产生周期性中断,利用视频包络和100 MHz时钟可形成50 MHz的DMA同步传送时钟,然后通过外部口DMA方式将

采样数据传送到DSP。ADC控制串行接口为通用三线串口,SPI总线接口实际上是一个串并转换器,可用于控制本振。本系统的DSP数据总线为

64位宽度,地址为32位。

由于雷达信号接收机中的信号处理量大,信号复杂,因此,通过基于高速大容量FPGA芯片的实时数据采集系统可以很好的满足对信号预处理的需要。

评论