Mentor工具被纳入台积电16纳米FinFET制程技术参考流程

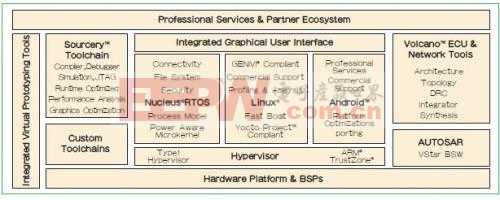

Mentor Graphics公司(纳斯达克代码:MENT)日前宣布它已完成其用于台积电16纳米FinFET制程的数字成套工具。台积电16纳米参考流程包含一些新功能,用于Olympus-SoC™布局与布线系统的16纳米设计,以及Calibre®物理验证和可制造性设计(DFM)平台。台积电和Mentor完成了V0.5设计规则手册(DRM)及SPICE 16纳米FinFET认证,并将继续进行V1.0的认证。

本文引用地址:https://www.eepw.com.cn/article/170352.htm“我们与Mentor Graphics紧密协作,以确定IC实施流程中要实现16纳米FinFET技术优势所需的新功能,”台积电公司设计基础架构营销事业部高级主管Suk Lee说。“Mentor在之前制程节点提供了稳定的设计支持环境,包括对多图案的支持、低功耗设计、光刻检查、可测试性设计,而新的功能正是建立于之前环境的基础之上。”

Mentor® Olympus-SoC布局与布线系统经过增强,可满足台积电16纳米设计支持与认证要求。支持FinFET设计的创新方法学有:有图案密度平面规划(实现早期金属填充密度检查)、MiM电容器插入(IR降改进)及对高电阻层布线/优化(实现更好品质的结果)。此外,Calibre InRoute™产品还让Olympus-SoC的客户能在设计中于本机调用Calibre DRC/DFM/DP签核引擎,从而更高效快速地实现制造闭合。

16纳米技术,特别是FinFET晶体管,引发了对更精确器件和互连寄生参数提取的需要。为确保客户16纳米设计的成功,台积电与Mentor合作,通过工具认证对Calibre xACT™产品进行加强,以提供高精确性、高性能的寄生参数提取。

Calibre YieldEnhancer产品在其SmartFill部件中提供了一些新功能,从而简化FinFET的填充规则并支持填充ECO流程,这样就能在满足高级填充签核要求的同时,更快更容易地闭合一项设计。

Calibre RealTime集成平台增加了一项支持:根据SPICE模拟生成的净电压进行16纳米电压依赖规则的自动检查,同时在Synopsys的Laker®定制设计环境中编辑版图。净电压在版图创建和编辑过程中,被自动施加于版图,从而实现精确的检查。Calibre RealTime和Synopsys Laker产品利用OpenAccess开放接口以实现快速流畅的用户体验,以在最少的时间内产生最佳的定制版图。

“每一个IC制程节点都带来新的挑战——自从20世纪60年代戈登摩尔提出著名的摩尔定律以来就一直是这样,”Mentor Graphics公司副总裁兼Design-to-Silicon总经理Joseph Sawicki说。“但是当我们逼近CMOS尺寸的极限时,每一新节点都需要更多的创新和与整个生态系统更紧密的协作,才能保持我们行业健康的发展步伐。Mentor和台积电再一次迎难而上,及时给行业带来了需要的技术。”

电容器相关文章:电容器原理

评论