- 移动应用、基础设施与航空航天、国防应用中 RF 解决方案的领先供应商 Qorvo®近日宣布推出新一代 1200V 碳化硅 (SiC) 场效应晶体管 (FET) 系列,该系列具有出色的导通电阻特性。全新 UF4C/SC 系列 1200V 第四代 SiC FET 非常适用于主流的 800V 总线架构,这种架构常见于电动汽车车载充电器、工业电池充电器、工业电源、DC/DC 太阳能逆变器、焊接机、不间断电源和感应加热等应用。UnitedSiC/Qorvo 功率器件总工程师 Anup Bhalla 表示:“我们通过

- 关键字:

Mentor P Qorvo SiC FET

- 简介虽然产品可靠性一直以来都是半导体行业的一个重要因素,但随着交通运输、医疗设备和 通信等领域越来越多地使用电子设备,对于能够在设计的产品寿命期内按预期工作的集成 电路 (IC) 的需求已呈现出指数级增长趋势。然而,尽管对于精准的可靠性验证的需求已显 著增长,但使用现有的验证技术确保 IC 可靠性一直是 IC 设计公司面临的重大挑战之一。技 术节点尺寸的缩减加上不同类型的设计应用的快速增长,让该问题变得更加复杂,增加了 需要的可靠性检查数量及其复杂性。所有这些因素都在有力地推动对于准确的自动化芯片 可靠性

- 关键字:

EDA Mentor Calibre

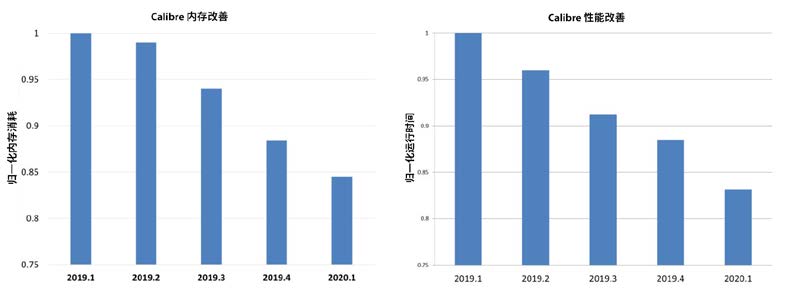

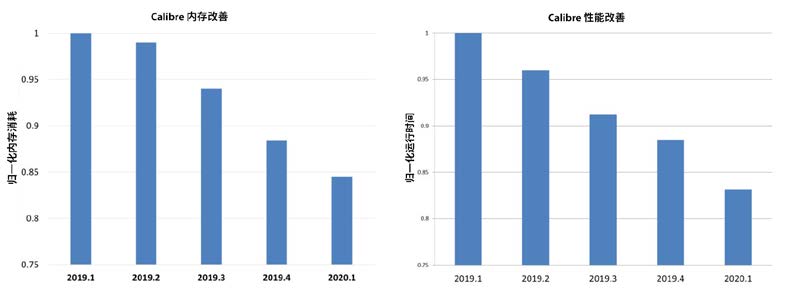

- 如果将部分或全部电子设计自动化 (EDA) 计算转移到云上,设计公司将能获得灵活的资源和 规模经济性,从而缩短产品上市时间并加快创新速度。Mentor, a Siemens Business (Mentor) 与 Advanced Micro Devices, Inc. (AMD) 和 Microsoft Azure (Azure) 合作,展示了 Calibre™ 平台 结合云计算如何能够提供更多计算资源,大幅缩短设计收敛时间,让设计更快上市。采用 7nm 量产设计,物理验证周期缩短了 2.5 倍。CAL

- 关键字:

MENTOR AMD MICROSOFT 云上EDA

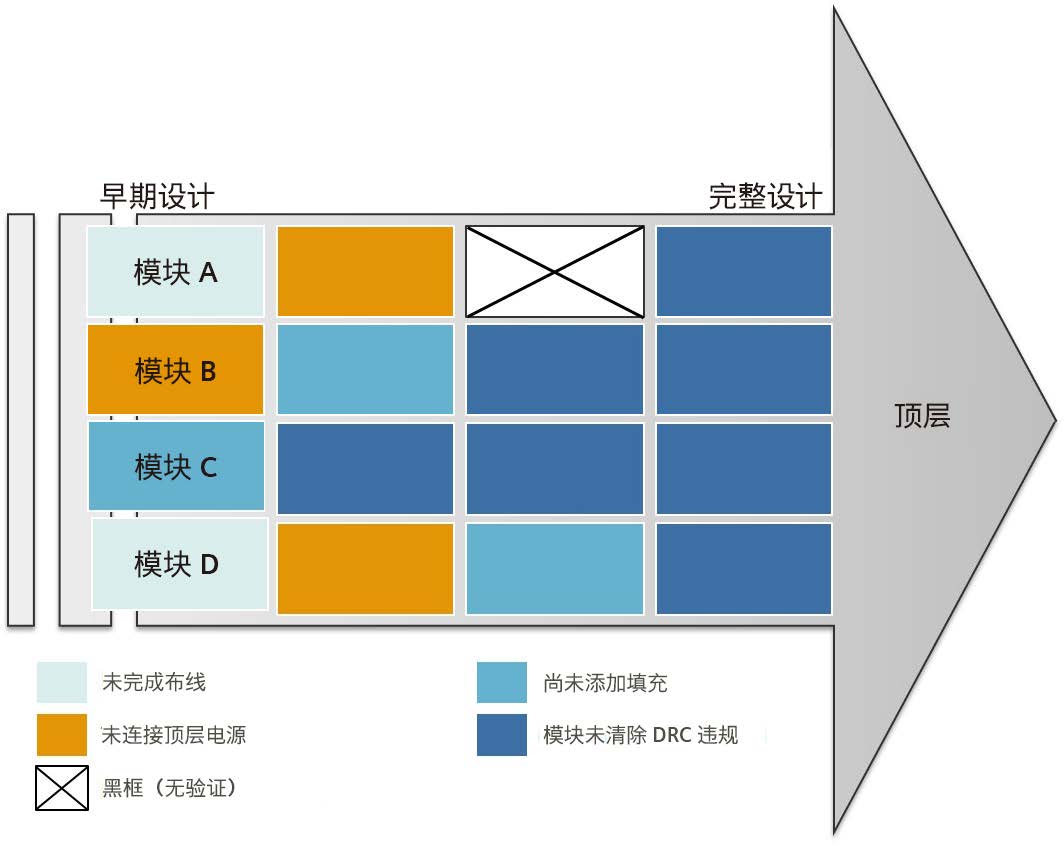

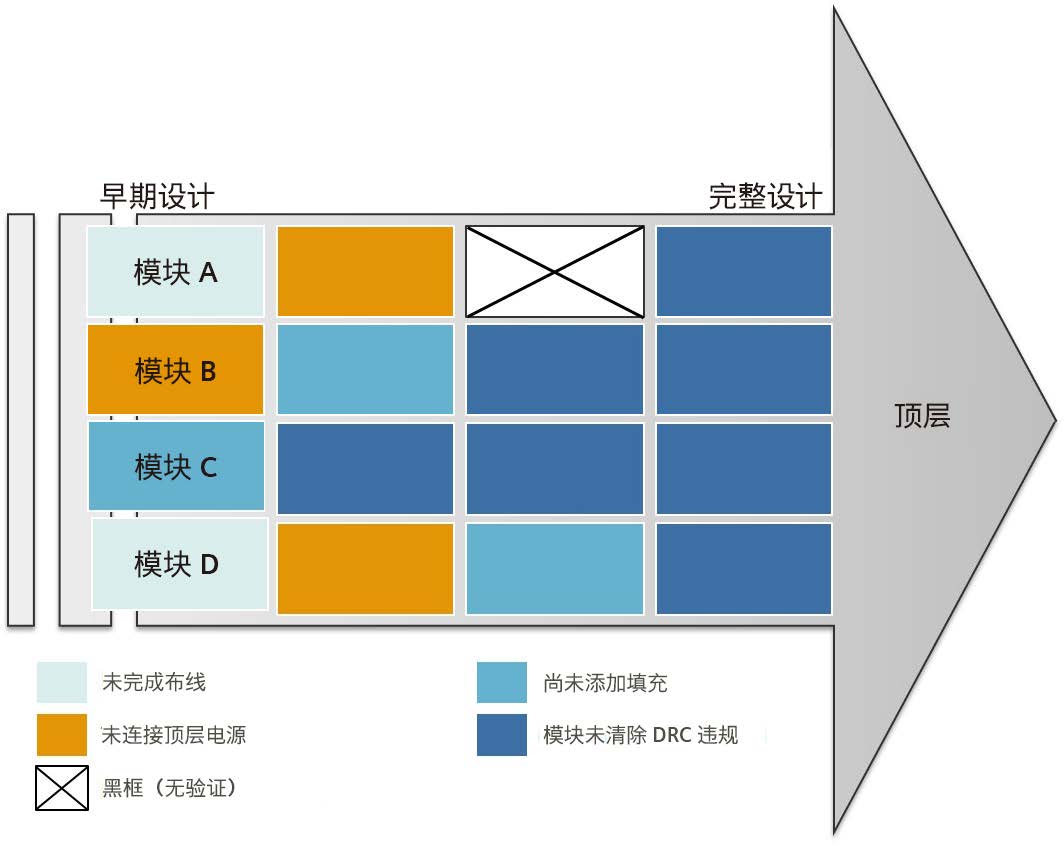

- 背景1981 年是业界公认的电子设计自动化 (EDA) 商业化元年,Mentor, a Siemens business 自这一年开始,长期致力于深耕 EDA 工具领域。从一开始,我们的 Calibre® 验证平台就专注于为企业提供一流的验证流程。 在与全球设计人员、工程师和团队的日常互动中,我们一直在密切观察设计和验证周期,并不断努力改 进我们的工具以提高生产率。有一个趋势非常明显……流片变得越来越困难,需要的时间也越来越长。根据行业会议调查得出的统计 数据,每年至少有 50% 的预定流片出现延迟。这些

- 关键字:

EDA Mentor Calibre

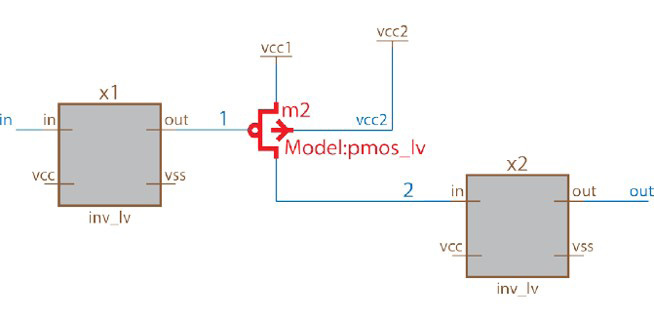

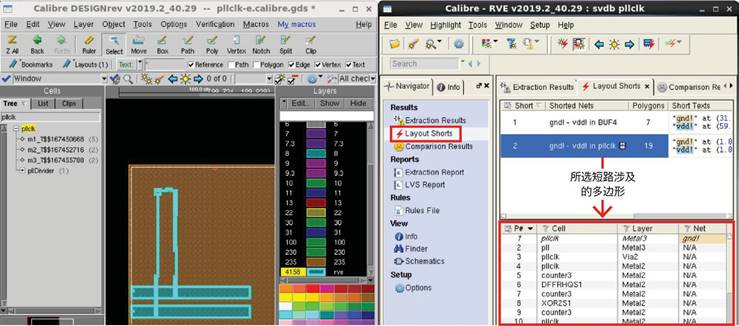

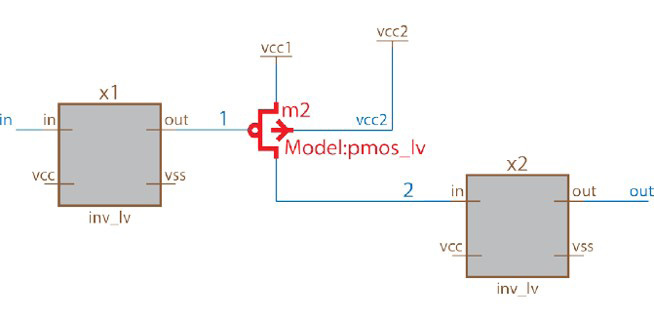

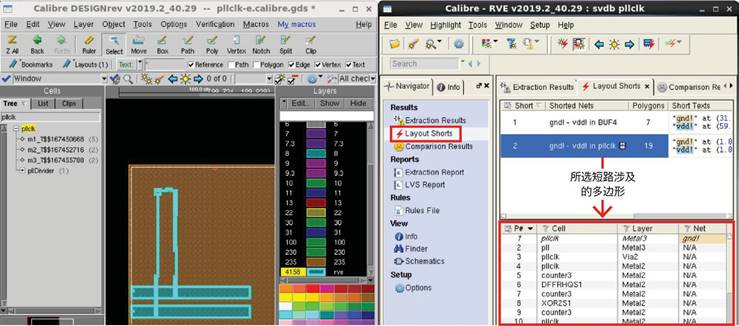

- 简介版图与电路图比较 (LVS) 验证是片上系统 (SOC) 设计周期中集成电路 (IC) 验证必不可少的组 成部分,但鉴于当今高密度且层次化的版图、不断提高的电路复杂性以及错综复杂的晶圆 代工厂规则,运行 LVS 可能是一项耗时且资源密集的工作。全芯片 LVS 运行不仅会将设计版 图与电路图网表进行比较,而且通常还包含会增加 LVS 运行时间的其他验证,例如电气规则 检查 (ERC) 和短路隔离。根据设计的复杂性,调试这些设计的 LVS 结果可能同样具挑战性且耗时,进而影响总周转时 间 (TAT) 和计

- 关键字:

LVS SOC IC设计 Mentor

- Mentor, a Siemens business 近日宣布与三星Foundry合作开发一款新的参考设计套件,旨在帮助双方共同客户简化在制造过程中对于先进芯片上系统嵌入式存储器的测试、诊断和维修。三星Foundry全新的设计解决方案套件 (SF-DSK) 采用了 Mentor 业界领先的 Tessent™MemoryBIST 软件技术,可帮助客户简化可测试性设计流程并提高产品良率。该套件包含一个用户友好的界面,将三星的 efuse 与 Tessent MemoryBIST 软件的内建自我修复功能连接在一

- 关键字:

Mentor 三星Foundry 存储器

- Mentor, a Siemens business 近日宣布,旗下系列IC设计工具获得了台积电(TSMC)业界领先的 N5 和 N6 制程技术认证。此外,Mentor 与 TSMC 的合作现已扩展到先进封装技术领域, Mentor Calibre™ 平台的 3DSTACK 封装技术将进一步支持 TSMC 的先进封装平台。TSMC 的 N5 和 N6 制程技术能够帮助众多全球领先的 IC 设计公司提高处理器的性能、缩小尺寸并降低功耗,从而更好地应对汽车、物联网、高性能计算、5G 移动/基础设施、

- 关键字:

Mentor 新思科 IC

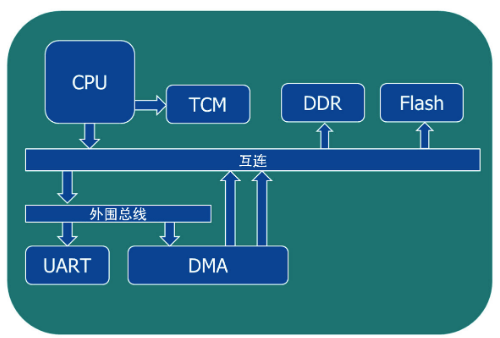

- 简介设计正变得日益复杂,越来越多的设计包含了处理器,甚至经常包含多个处理器。由于处理器是设计的不可分割的一部分,因此我们必须验证在处理器上运行的软件与设计的其他部分之间的交互,这一点非常重要。软件对当今系统的运作至关重要,因而在实验室中调通原型芯片之前,对硬件/软件边界的验证和确认不容出现任何延迟。至少,验证团队必须完成这项任务,并且自行承担风险。相信我们都听说过一些严重错误的场景,例如,团队在实验室中发现,处理器的总线与设计的连接顺序接反了,或者处理器在低功耗模式下再无法加电启动。硬件/软件逐步细化一个

- 关键字:

Mentor 处理器

- 西门子旗下业务Mentor 宣布推出一套全新的 Tessent? 软件安全生态系统,即由 Mentor与其行业领先合作伙伴携手提供的涵盖最优汽车 IC 测试解决方案的产品组合,该程序能够帮助 IC 设计团队满足全球汽车行业日益严格的功能安全需求。

- 关键字:

Mentor Tessent Safety 自动驾驶 IC 测试

- 王 莹 (《电子产品世界》,北京 100036) 编者按:科技日新月异的数字时代,人工智能/机器学习在半导体业的应用中快速增长。日前,Mentor公司ICEDA部门的掌舵人 Joseph Sawicki先生在“2019 Mentor论坛”北京站期间,谈了人工智能/机器学习在下一个10年带来的机遇,以及EDA设计和验证方法论和工具需要哪些新变革。 1 本土企业正在加快AI和机器学习的创新 Joseph最近拜访了中国的一家初创公司,该公司在2年前(2017年)刚成立,在大约6个月以前(2019年2月

- 关键字:

201910 AI Mentor

- Mentor, a Siemens business 日前宣布,人工智能 (AI) 芯片专业公司 Iluvatar CoreX 已在 Veloce™ Strato 硬件加速仿真平台上进行了标准化,以验证他们的 AI 云培训片上系统 (SoC) 芯片集和专有软件平台。Iluvatar CoreX 创立于 2015 年 12 月,旨在满足迅速发展的 AI 领域对可扩展型高性能芯片解决方案的日益增长的需求,为周边器件和基于云的应用程序实现高级人工智能。“Iluvatar 的解决方案利用超大规模并行计算架构的优势

- 关键字:

Iluvatar CoreX Mentor Veloce Strato 硬件加速仿真平台 AI芯片

- Mentor®, a Siemens business 今日宣布 Chips&Media™ 已成功部署 Mentor Catapult™

HLS 平台,将使用深度神经网络 (DNN) 算法设计和验证其 c.WAVE 计算机视觉 IP 的实时对象检测。Chips&Media

是一家面向片上系统 (SoC) 设计高性能、高质量视频 IP 的领先供应商,其产品广泛应用于汽车、监控和消费电子领域。 Chips&Media

需要通过减少功能验证时间、时序收敛、自定义和最终优

- 关键字:

Mentor DNN

- 除了引入 ATE-Connect 技术之外,Mentor 的 Tessent 部门还宣布与 Teradyne 及其他重要客户开展合作,以验证整个解决方案。Teradyne 是面向测试和工业应用的自动化设备的领先供应商。Mentor 的Tessent工具与 ATE-Connect 以及UltraFLEX的 Teradyne PortBridge 相结合,这使得DFT 开发环境能够直接与 Teradyne UltraFLEX 通信,实现 IP 模块的交互调试,因此测试调试效率的显著提升。 “Terady

- 关键字:

Mentor Teradyne

- Mentor, a Siemens business 今日宣布 Mentor Calibre® nmPlatform 和 Analog FastSPICE™ (AFS™) Platform 获得 TSMC 的 7nm FinFET Plus 和最新版本的 5nm FinFET 工艺的认证。此外,Mentor 还继续扩展 Xpedition™ Package Designer 和 Xpedition Substrate Integrator 产品的功能,以支持 TSMC 的高级封装产品。 TSMC 设

- 关键字:

Mentor FinFET

mentor介绍

Mentor Graphics® 是电子设计自动化技术的领导产商,它提供完整的软件和硬件设计解决方案,让客户能在短时间内,以最低的成本,在市场上推出功能强大的电子产品。当今电路板与半导体元件变得更加复杂,并随着深亚微米工艺技术在系统单芯片设计深入应用,要把一个具有创意的想法转换成市场上的产品,其中的困难度已大幅增加;为此 Mentor提供了技术创新的产品与完整解决方案,让工程师得以 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473