关于Micron和Intel 20nm 64-Gbit MLC NAND闪存的深度探究

NAND闪存在半导体市场上的成功主要得益于手机和平板电脑市场的持续迅猛发展以及高性能固态硬盘(SSDs)取代硬盘驱动器的广泛应用。美光与英特尔去年共同宣布,通过20 nm制造工艺技术结合突破性的单元架构概念,可以制造出仅由一组简单芯片组成的TB容量NAND闪存。

本文引用地址:https://www.eepw.com.cn/article/133125.htm过去几年,NAND闪存因为出色的物理扩展性和每个单元两到三个字节的多层单元(MLC)搭载方式,在众多高密度商业内存中享誉最高。然而近期便携式电子产品对于NAND闪存的大量需求,导致NAND闪存必须大幅缩小器件架构以获得更高的密度和更快的速度,并消耗更低的单字节成本。NAND闪存单元尺寸的大幅缩减在传统的20 nm级浮栅闪存单元架构下,必然会遇到巨大障碍。

面对以上提及的这些难题,英特尔与美光负责工艺制程开发的合资公司——英特尔美光闪存科技(IMFT)一直在积极寻求缩小NAND单元尺寸的方法,并最终成功开发和制造了第一个20nm设计规格下的高密度多层级NAND闪存。通过全平面浮栅单元设计的引入,IMFT也发明了全新的闪存架构。作为公认的NAND闪存制造工艺业内的领军企业,IMFT引入了结合高K/金属栅(HKMG)叠层技术的单元架构平坦化工艺。这种工艺可以攻克在20 nm及以下尺寸缩减过程中面临的许多物理和电子方面难题。

为了更好的了解这种先进的工艺和全新的单元架构,UBM TechInsights(http://www.ubmtechinsights.com/

在64-Gbit多层单元NAND闪存的制造过程中,20 nm加工技术的引入让IMFT奠定了在新制程节点中的领导地位。这种NAND芯片面积只有117 mm2,比IMFT现存的25 nm 64 Gbit NAND闪存在面积上减少了近30%,这成为其一大特色。IMFT的64-Gbit NAND闪存是由单层多晶、金属栅和三层金属制造的,呈48-pin无铅TSOP封装。64-Gbit闪存单一芯片分成四个bank加上一个单边焊盘,与之前芯片面积为162 mm2的25 nm 64 Gbit NAND闪存相比,存储区效率达到了52%。

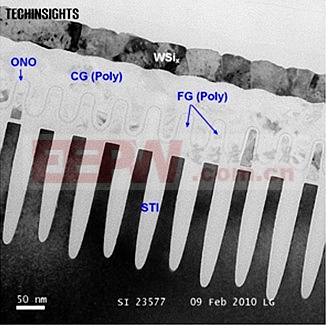

在传统的NAND浮栅单元上,控制栅(CG)和绝缘膜缠绕在浮栅(FG)上,耦合系数很大程度上依赖于浮栅侧壁,如下图所示:

传统浮栅NAND(IMFT 25 nm NAND闪存)

深度探究

对于20nm级及其以下的工艺节点来说,单元空间已经很窄,控制栅无法插在浮栅之间。因此,NAND闪存只能采用平面化单元的结构,而不再让控制栅和浮栅缠绕在一起。

评论