富士通和SuVolta展示低电压工作的SRAM模块

富士通半导体和SuVolta宣布,通过将SuVolta的PowerShrink低功耗CMOS与富士通半导体的低功耗工艺技术集成,已经成功地展示了在0.425V超低电压下,SRAM(静态随机存储)模块可以正常运行。这些技术降低能耗,为即将出现的终极“生态”产品铺平道路。技术细节和结果将会在12月5日开始在华盛顿召开的2011年国际电子器件会议(IEDM)上发表。

本文引用地址:https://www.eepw.com.cn/article/126801.htm从移动电子产品到因特网共享服务器,以及网络设备,控制功耗成为增加功能的主要限制。而供应电压又是决定功耗的重要因素。之前,CMOS的电源电压随着器件尺寸减小而稳定下降,在130nm技术结点已降至大约1.0V。但在那之后,技术结点已缩小到28nm,电源电压却没有随之进一步降低。电源供应电压降低的最大障碍是嵌入的SRAM模块最低工作电压。

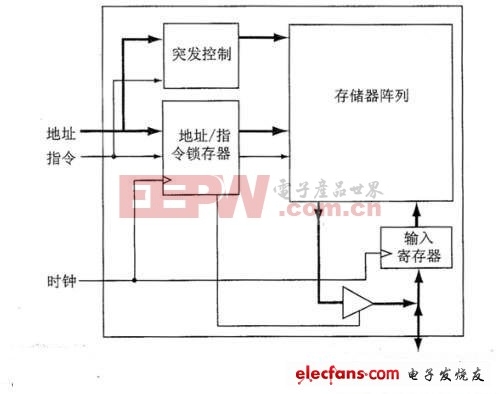

结合SuVolta的Deeply Depleted Channel (DDC)晶体管技术 – 该公司的PowerShrink平台组件之一 – 与富士通半导体的尖端工艺,两家公司已经证实通过将CMOS晶体管临界电压(VT)的波动降低一半,576Kb的SRAM可在0.4伏附近正常工作。该项技术与现有设施匹配良好,包括现有的芯片系统(SoC)设计布局,设计架构比如基体偏压控制,以及制造工具。

背景

遵循微缩定律,在130nm技术结点CMOS电源供应电压逐步降低到大约1.0V。但是,尽管工艺技术已经由 130nm继续缩小到28nm,电源电压却还保持在1.0V左右的水平。由于动态功率与供应电压的平方成正比,能耗已经成为CMOS技术的主要问题。电压降低止步于130nm结点的原因是多处波动来源,包括随机杂质扰动(RDF)。RDF是器件及工艺波动的一种形式,由注入杂质浓度或晶体管通道内掺杂原子 的扰动引起。RDF导致同一芯片上不同晶体管的临界电压(VT)出现偏差。

已见报道的两种特殊结构可以成功减小RDF:ETSOI和Tri-Gate – FinFET技术的一种。但是,这两种技术都非常复杂,使得他们很难与现有设计和制造设施匹配。

降低SRAM最低工作电压

对于大多数芯片,降低供应电压的限制来自于SRAM。如图2所示,富士通半导体和SuVolta展示了在低至0.425V电压下仍然能够正常工作的SRAM模块。由于SRAM是降低供应电压最大的挑战,该项成果意味着DDC将使得多种基于CMOS的电路在0.4V左右运作成为现实。

总结与未来计划

DDC晶体管的工艺流程已经成功建立。所制造的DDC晶体管显示VT波动比基准流程改善了50%,并且产出在0.425V电压下仍能运作的SRAM,充分证明了DDC晶体管有能力将供应电压降低到0.4V左右。

富士通半导体将发展这项技术并积极回应客户在消费电子产品,移动设备及其他领域对于低功耗/低电压运行的要求。

评论