- IT之家 2 月 22 日消息,英特尔于北京时间今天凌晨 0 点 30 分举办了 IFS Direct Connect 2024,在宣布 IFS 更名为 Intel Foundry 之外,还公布了未来十年的工艺路线图,尤其提及了 1.4nm 的 Intel 14A 工艺。英特尔在本次活动中宣布了大量的动态信息,IT之家梳理汇总如下:图源:IntelIFS 更名为 Intel Foundry英特尔首席执行官帕特・基辛格(Pat Gelsinger)在本次活动中,宣布 Intel Foundry S

- 关键字:

英特尔 EDA 工艺

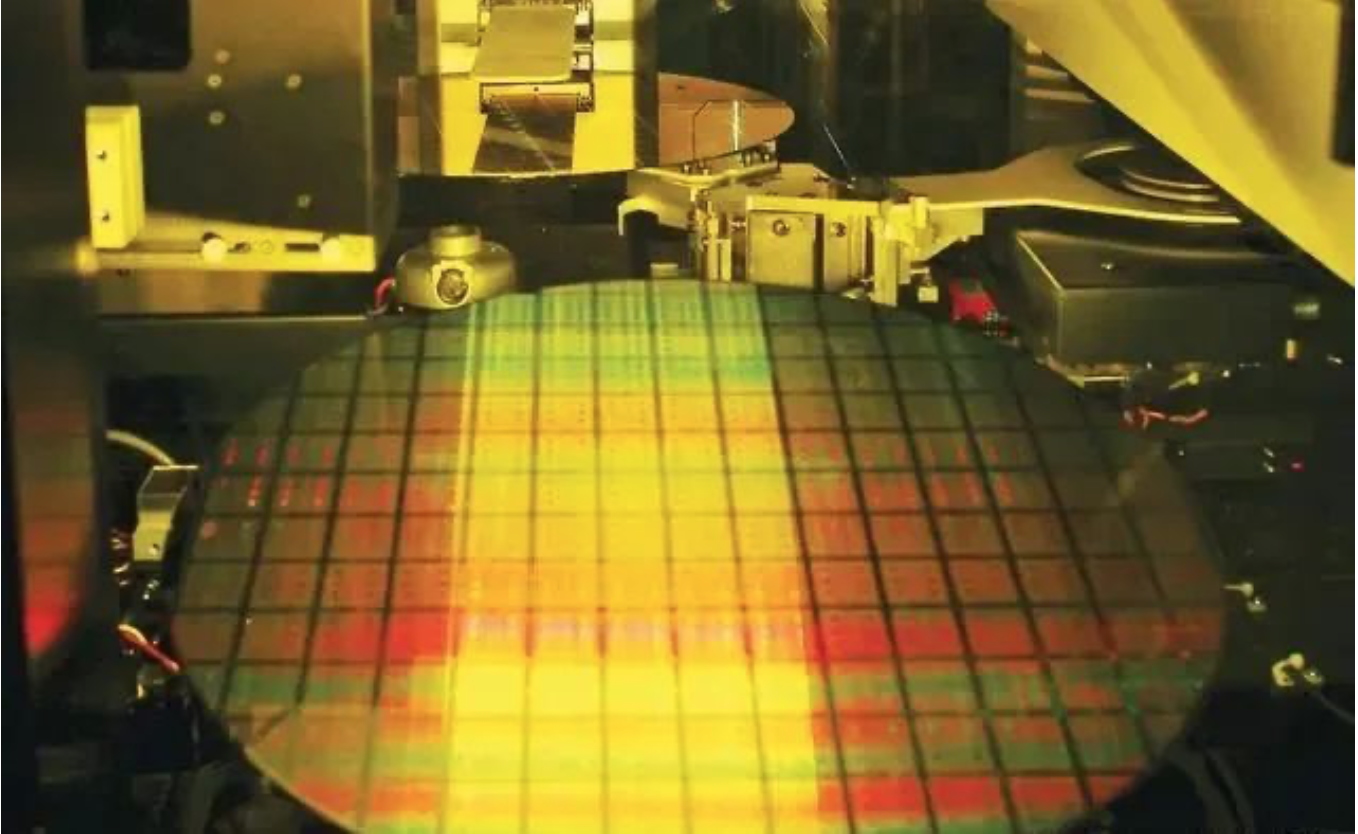

- 2023年,随着美国技术制裁的升级,中国半导体行业面临着严峻的挑战,美国对先进芯片制造工具和人工智能处理器的限制更加严格。10月,美国扩大了对半导体晶圆制造设备的出口管制,从战略上限制了中国对较不先进的英伟达数据中心芯片的获取。此举是遏制中国技术进步的更广泛努力的一部分,成功说服日本和荷兰加入限制先进半导体工具出口的行列。这些制裁暴露了中国芯片供应链的脆弱性,促使中国加大力度实现半导体自给自足。国家资金支持国内生产较不先进的工具和零件的举措,取得了显著进展。然而,在开发对先进集成电路至关重要的高端光刻系统

- 关键字:

中国 半导体 工艺

- 10月31日消息,苹果举行新品发布会,线上发布M3系列芯片(M3、M3 Pro以及M3 Max),除了芯片更新苹果还带来了搭载M3系列芯片的MacBook Pro以及24英寸版iMac。这是苹果首次将Pro与Max首次与基础款同时公布,苹果官方在发布会中也表示:这一系列的芯片采用了最新的3nm工艺制程,意味着比当前的M2系列将要「快得吓人」。M3系列芯片信息:M3配备8核CPU,10核GPU,24GB统一内存,速度最高比M2提升20%M3 Pro配备12核CPU,18核GPU,36GB统一内存,速度最高比

- 关键字:

苹果 M3 芯片 3nm 工艺 GPU

- 据武汉市科技局官微消息,日前,半导体芯片生产中的重要工艺设备——“薄膜生长”实验装置在武汉通过验收,这项原创性突破可提升半导体芯片质量。据悉,半导体薄膜生长是芯片生产的核心上游工艺。这套自主研制的“薄膜生长”国产实验装置,由武汉大学刘胜教授牵头,联合华中科技大学、清华大学天津高端装备研究院、华南理工大学、中国科学院半导体研究所、中国科学院微电子研究所等多家单位,历时5年完成。这套“薄膜生长”国产实验装置由“进样腔”、“高真空环形机械手传样腔”等多个腔体和“超快飞秒双模成像系统”、“超快电子成像系统”等多个

- 关键字:

半导体 薄膜生长 工艺

- ● 介绍随着技术推进到1.5nm及更先进节点,后段器件集成将会遇到新的难题,比如需要降低金属间距和支持新的工艺流程。为了强化电阻电容性能、减小边缘定位误差,并实现具有挑战性的制造工艺,需要进行工艺调整。为应对这些挑战,我们尝试在1.5nm节点后段自对准图形化中使用半大马士革方法。我们在imec生产了一组新的后段器件集成掩膜版,以对单大马士革和双大马士革进行电性评估。新掩膜版的金属间距分别为14nm、16nm、18nm、20nm和22nm,前两类是1.5nm节点后段的最小目标金属间距

- 关键字:

半大马士革 后段器件集成 1.5nm SEMulator3D

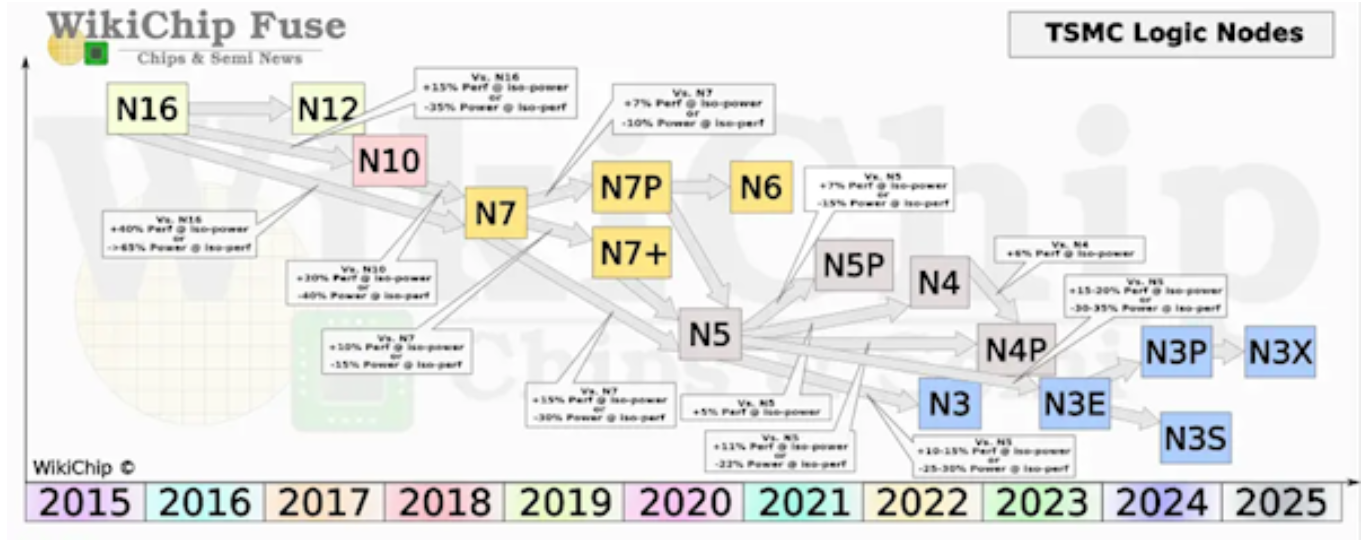

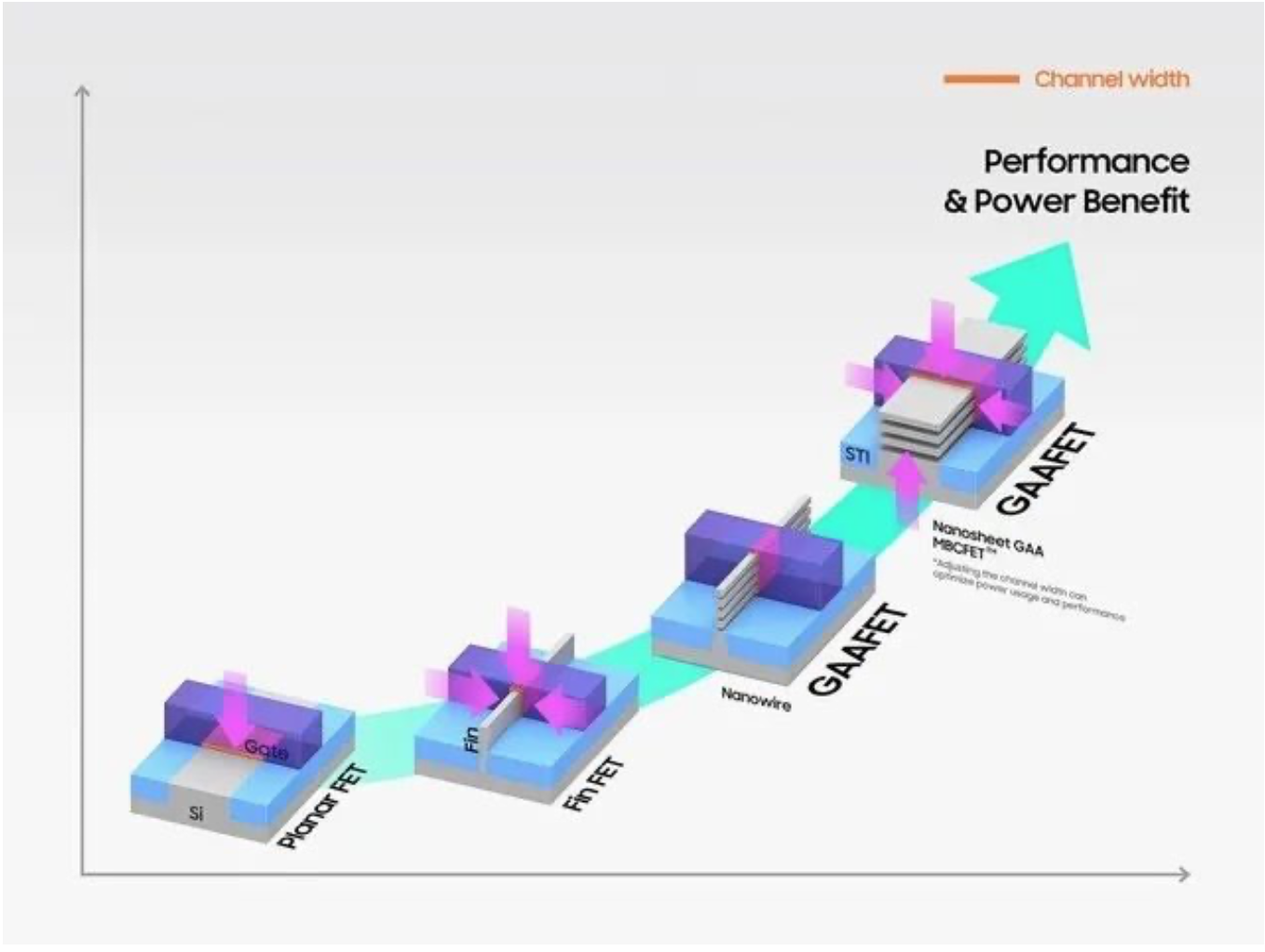

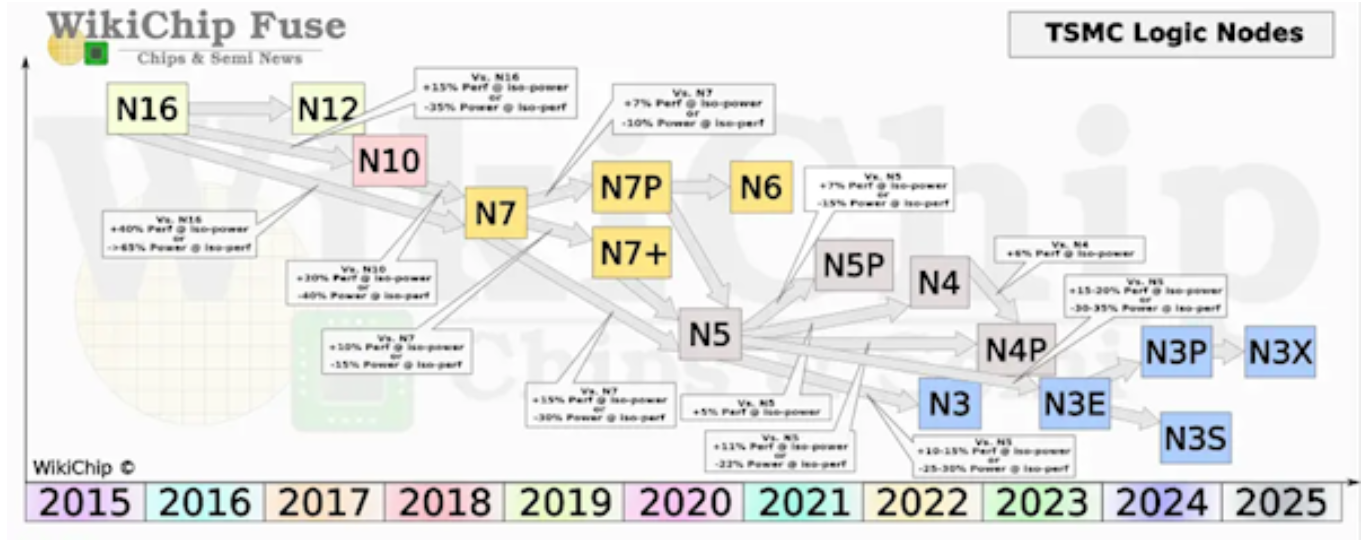

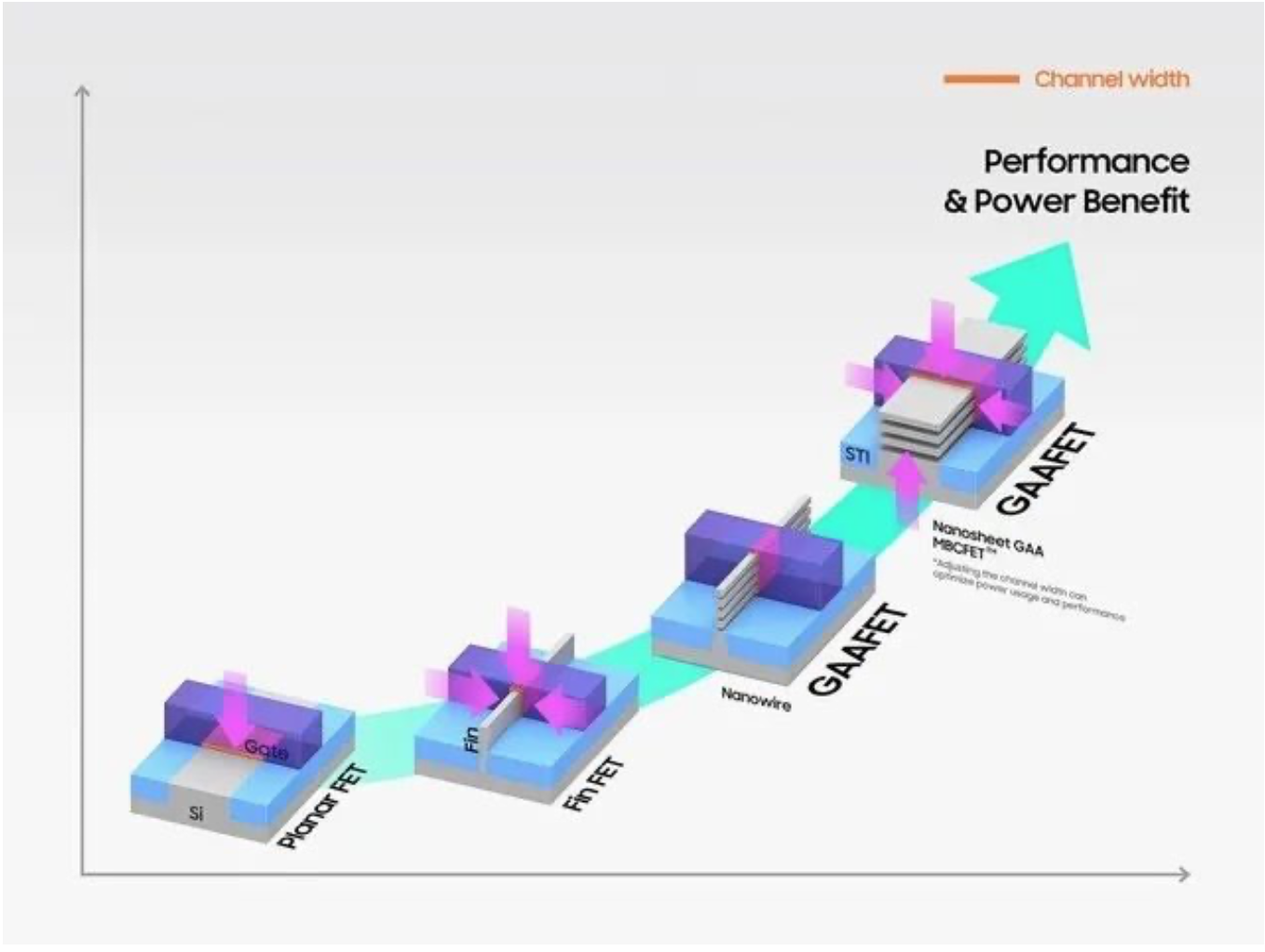

- 目前三星和台积电(TSMC)都已在3nm制程节点上实现了量产,前者于2022年6月宣布量产全球首个3nm工艺,后者则在同年12月宣布启动3nm工艺的大规模生产,苹果最新发布的iPhone 15 Pro系列机型上搭载的A17 Pro应用了该工艺。据ChosunBiz报道,虽然三星和台积电都已量产了3nm工艺,不过两者都遇到了良品率方面的问题,都正在努力提高良品率及产量。三星在3nm工艺上采用下一代GAA(Gate-All-Around)晶体管技术,而台积电沿用了原有的FinFET晶体管技术,无论如何取舍和选

- 关键字:

三星 台积电 工艺 3nm

- 据外媒报道,苹果已经预订了台积电3nm制程工艺今年的全部产能,用于代工iPhone 15 Pro系列搭载的A17仿生芯片和新款13英寸MacBook Pro等将搭载的M3芯片。1据悉,最初台积电分配了约10%的3nm产线来完成英特尔芯片的订单。然而由于设计延迟,英特尔决定推迟其计划外包给台积电的下一代中央处理器(CPU)的量产,这导致台积电3nm制程工艺最初的生产计划被打乱。与此同时,最新消息称已预订了台积电3nm制程工艺今年全部产能的苹果,也削减了订单,所以台积电3nm制程工艺在四季度的产量预计将由此前

- 关键字:

苹果 英特尔 台积电 3nm 工艺

- 苹果将继续在今年9月举办一年一度的秋季新品发布会,届时全新的iPhone 15系列将正式与大家见面,不出意外的话该系列将继续推出包含iPhone 15、iPhone 15 Plus、iPhone 15 Pro和iPhone15 Pro Max四款机型,将在不同程度上带来升级,尤其新一代的A17芯片早就成为大家关注的焦点。根据此前曝光的消息,全新的iPhone 15系列将继续提供与iPhone 14系列相同的四款机型,并且仍然有着明显的两极分化。其中两个Pro版将会配备ProMotion显示屏,屏幕亮度进一

- 关键字:

苹果 A17 处理器 3nm 工艺 芯片 效能

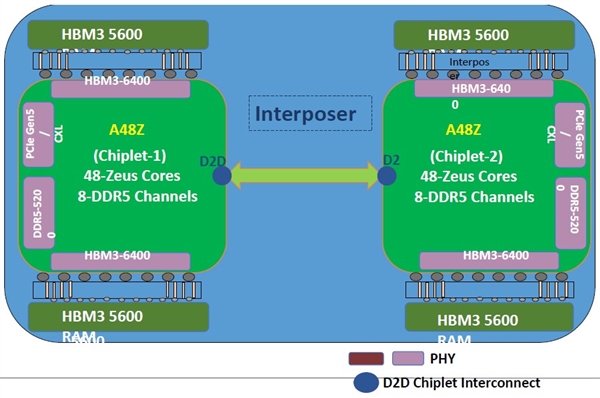

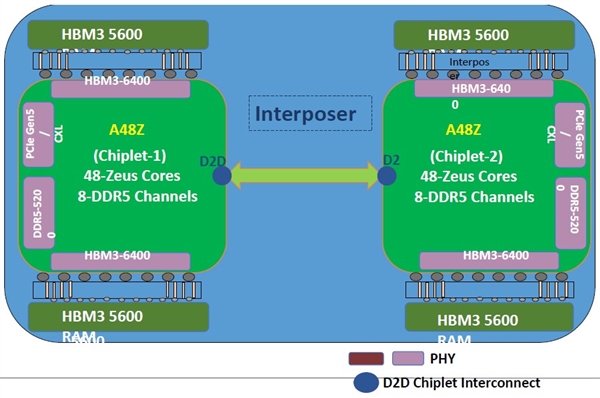

- 5月22日消息,在半导体领域,印度也燃起了雄心,此前没啥基础的他们都要励志在5年内做全球第一的半导体大国,而且全产业链发展,印度高性能计算中心C-DAC本周就公布了自己研发的Aum HPC处理器,最多96核,而且是5nm工艺。在高性能计算市场,ARM处理器近年来确实取得了一些成绩,富士通研发的48核A64FX处理器之前还成为TOP500超算第一,NVIDIA也有72核到144核的Grace处理器,Ampere公司之前推出了80核的ARM处理器。这几天Ampere还推出了新一代的云数据中心处理器“Amper

- 关键字:

印度 96核 5nm

- 5月4日消息,集邦咨询最新的一份报告指出,去年10月,美国商务部对中国实施新的禁令,不允许进口18nm及更先进工艺的DRAM内存芯片制造设备,对于厂商的布局也产生了深远影响。SK海力士位于无锡的工厂虽然获得了一年的宽限期,但考虑到未来风险,以及市场需求疲软, SK海力士选择在2023年第二季度将无锡工厂的月产能削减30%。SK海力士原计划将无锡工厂的制造工艺从1Ynm升级为1Znm,并减少“成熟工艺”的产能。但在美国禁令发出后, SK海力士选择了提高21nm成熟工艺的产能,并专注于DD

- 关键字:

SK海力士 存储 工艺

- 在7nm、5nm等先进制程工艺上率先量产的台积电,也被认为有更高的良品率,但在量产时间晚于三星近半年的3nm制程工艺上,台积电可能遇到了良品率方面的挑战,进而导致他们这一制程工艺的产能提升受到了影响。

- 关键字:

台积电 3nm 工艺 良品率

- 三星似乎已经解决了4nm工艺的一系列障碍。据Digitimes报道,三星在第三代4nm工艺的进步可能超出外界预期,从之前的60%提高到70%以上。

- 关键字:

三星 4nm 制程 工艺 良品率 台积电 苹果

- 据《科创板日报》报道,针对“因4~5纳米先进制程良率逐渐稳定,客户订单正逐渐增加,稼动率也相应反弹,12英寸稼动率回升至九成。”这一市场消息,三星半导体对其进行了回应。报道指出,三星半导体相关负责人回应表示,“暂无法透露最新良率或者客户情况。正如我们在2022年4月的财务电话会议上所提及,5nm制程良率自去年年初以来已稳定下来,而4nm制程良率也已得到了提升,自2022年第一季度以来一直在预期的轨道上。自此4~5nm制程良率已经稳定了。”据韩国媒体BusinessKorea报道,三星4纳米制程良率相较之前

- 关键字:

5nm 良率 晶圆代工 三星

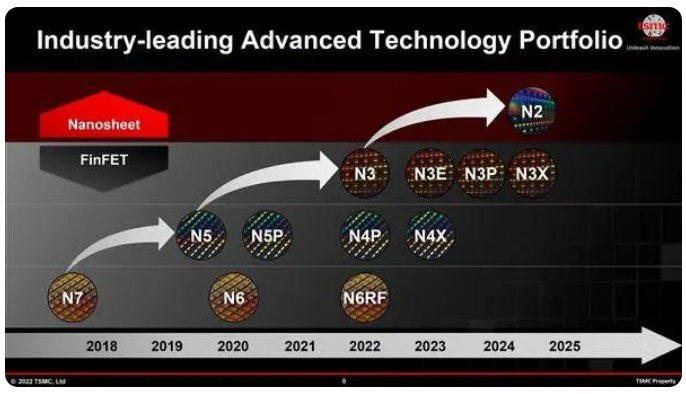

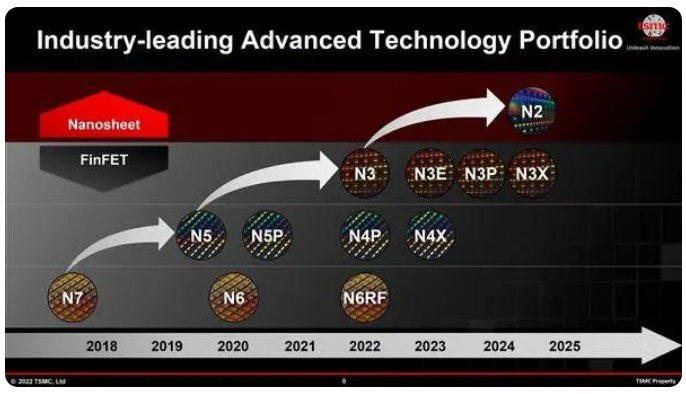

- 最新消息称,除了苹果iPhone 15系列所搭载的A17之外,苹果新款MacBook Air、iPad Air/Pro预计将采用台积电的N3E工艺制造的M3芯片,这些搭载新芯片的产品可能会分别在今年下半年和明年上半年陆续推出。此前,有报道称新款15英寸MacBook Air将采用与2022年13英寸MacBook Pro一起推出的M2芯片。然而,据爆料称苹果新款MacBook Air可能会搭载M3处理器性能,相比于M2 Max提升24%(单核)和6%(多核),但可能无缘在6月6日的苹果WWDC开发者大会上

- 关键字:

苹果 M3 芯片 台积电 N3E 工艺

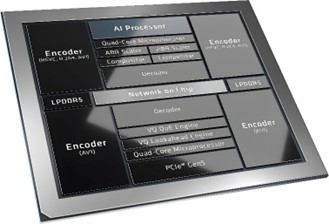

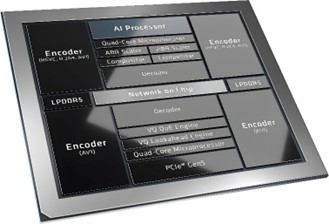

- 2023 年 4 月 6 日,加利福尼亚州圣克拉拉 — AMD (超威,纳斯达克股票代码:AMD)今日宣布推出 AMD Alveo™ MA35D 媒体加速器,该卡具备两个 5 纳米基于 ASIC 的、支持 AV1 压缩标准的视频处理单元( VPU ),专为推动大规模直播互动流媒体服务新时代而打造。随着全球视频市场超 70% 的份额由直播内容主导1,一类新型的低时延、大容量交互式流媒体应用正在涌现,例如连线观赏、直播购物、在线拍卖和社交流媒体。 AMD Alveo MA35D 媒体加速器Alveo

- 关键字:

AMD 5nm ASIC 媒体加速器卡 大规模交互式流媒体服务

5nm 工艺介绍

您好,目前还没有人创建词条5nm 工艺!

欢迎您创建该词条,阐述对5nm 工艺的理解,并与今后在此搜索5nm 工艺的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473