台积电公布N2 2nm缺陷率:比3/5/7nm都要好

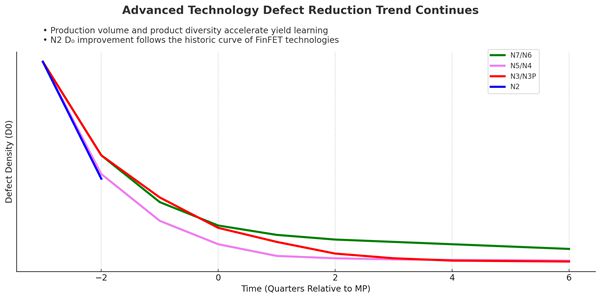

4月26日消息,在近日举办的北美技术论坛上,台积电首次公开了N2 2nm工艺的缺陷率(D0)情况,比此前的7nm、5nm、3nm等历代工艺都好的多。

本文引用地址:https://www.eepw.com.cn/article/202504/469869.htm台积电没有给出具体数据,只是比较了几个工艺缺陷率随时间变化的趋势。

台积电N2首次引入了GAAFET全环绕晶体管,目前距离大规模量产还有2个季度,也就是要等到年底。

N2试产近2个月来,缺陷率和同期的N5/N4差不多,还稍微低一点,同时显著优于N7/N6、N3/N3P。

从试产到量产半年的时间周期内,N7/N6的综合缺陷率是最高的,N3/N3P从量产开始就低得多了,N5/N4情况更好,从试产开始就明显更低。

N2如果能延续N5/N4的趋势,前景无疑是非常光明的。

台积电还指出,一种工艺的缺陷率能否快速降低,除了取决于本身的设计和技术,也要看制造芯片数量、产能规模,越多越大就越容易发现缺陷并改进。

台积电N2已流片的芯片数量就明显更多,也是其能够快速降低缺陷率的关键原因。

评论