纳米压印:一个「备胎」走向「台前」的故事

佳能在 10 月 13 日宣布,正式推出纳米压印半导体制造设备。对于 2004 年就开始探索纳米压印技术的佳能来说,新设备的推出无疑是向前迈出了一大步。佳能推出的这个设备型号是 FPA-1200NZ2C,目前可以实现最小线宽 14nm 的图案化,相当于生产目前最先进的逻辑半导体所需的 5 纳米节点。

本文引用地址:https://www.eepw.com.cn/article/202310/452048.htm佳能表示当天开始接受订单,目前已经向东芝供货。

半导体行业可谓是「苦光刻机久已」,纳米压印设备的到来,让期盼已久的半导体迎来一线曙光。那么什么是纳米压印技术?这种技术距离真的能够取代光刻机吗?

纳米压印走向台前

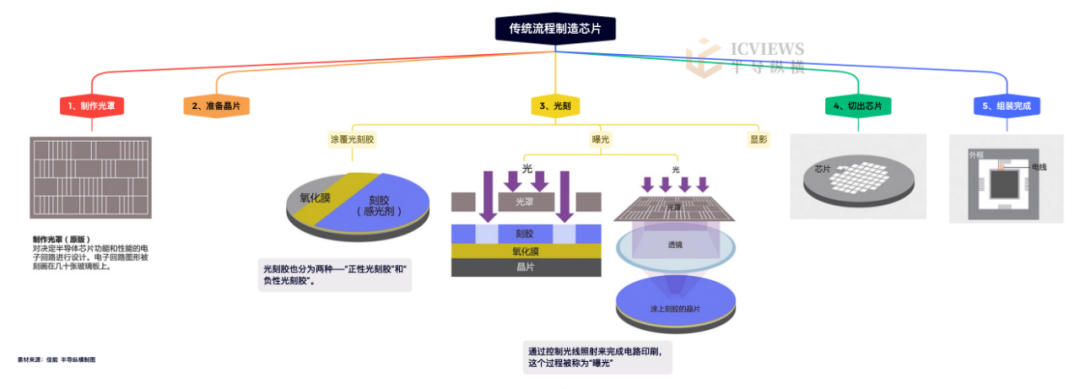

想要了解纳米压印到底解决了什么问题,先从了解传统芯片制造方式开始。传统的芯片制造方式,先是从半导体晶硅中切割出很薄的圆形晶片,反复进行成膜、曝光、显影、注入负离子等处理,从而生产出半导体芯片。

一开始是制作光罩,也就是对电子回路进行设计,把决定芯片功能和性能的电子回路刻画在几十张玻璃板上。

之后准备圆形的晶片,将其作为制作芯片的胚子,加热晶片使得其表面形成氧化膜,然后涂上光刻胶。光刻胶通过改变化学性质的方式让晶圆成为「相纸」。晶圆表面的光刻胶层越薄,涂覆越均匀,可以印刷的图形就越精细。

根据光(紫外线)反应性的区别,光刻胶可分为两种:正胶和负胶,前者在受光后会分解并消失,从而留下未受光区域的图形,而后者在受光后会聚合并让受光部分的图形显现出来。

在晶圆上覆盖光刻胶薄膜后,就可以通过控制光线照射来完成电路印刷,这个过程被称为「曝光」。曝光之后的步骤是在晶圆上喷涂显影剂,目的是去除图形未覆盖区域的光刻胶,从而让印刷好的电路图案显现出来。

这其中,涂覆光刻胶、曝光和显影三个步骤属于光刻,所以简单来讲,光刻就是利用光线将电路图案「印刷」到晶圆上。

光刻机处理一个晶片,不是一次能完事的,基本会来好几次,有时要多重曝光,要上十次。因此,光刻是芯片制造过程中最重要、最复杂也最昂贵的工艺步骤,其成本占总生产成本的 30% 以上,同时占据了将近 50% 的生产周期。

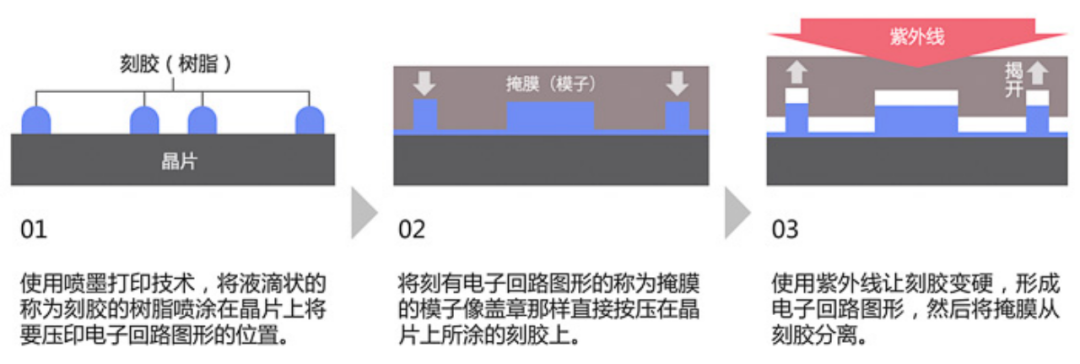

纳米压印替代的就是光刻环节。以往的设备就是采用「光」来刻电子回路图形,而纳米压印就是把电子回路图形像「盖章」那样盖上。

来源:佳能

把液滴状的刻胶(树脂)涂到晶片上,然后将掩膜按压(压印)在刻胶上,并重复叠加进行此种按压。这之后经过将掩膜从刻胶分离的「离模」工序,作出电路图形。也就是之前的制作过程是「非接触」,现在变成了「接触」。

这其中有多个好处。第一个,降低成本。既然不需要「光」进行刻绘,那么就不需要复杂的光路系统和昂贵的光源。此外,如果使用光刻技术,光刻后还附加了很多额外的处理步骤(包括额外的光刻、沉积、刻蚀),如果无需光刻,那么这些步骤带来的成本也将省下。

佳能的研究显示,其设备在每小时 80 片晶圆的吞吐量和 80 片晶圆的掩模寿命下,纳米压印光刻相对 ArF 光刻工艺可降低 28% 的成本,随着吞吐量增加至每小时 90 片,掩模寿命超过 300 批次,成本可降低 52%。

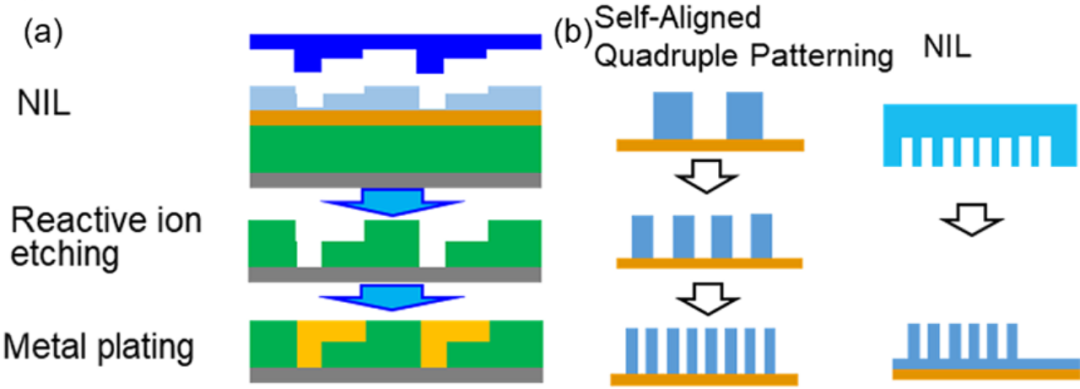

第二个,模板设计更简单。无需光刻机使用的掩膜版图案设计,压印出来的图案尺寸完全由模板上的图案决定,所以不会受到传统光刻胶技术中光源波长、光学衍射的限制和影响。纳米压印技术只要预先在掩膜上制作好图案,即使是复杂结构也能一次性形成,同时也避免了传统光刻工艺中的多次重复曝光。

图 (a) 使用 NIL 的 3D 图案化,(b)SAQP(自对准四重图案化)和 NIL 在一维精细图案化中的比较

第三个,与光学光刻相比,纳米压印则是将形成三维结构的掩膜压在晶圆上被称为液体树脂的感光材料上,同时照射光线,一次性完成结构的转印。传统的光刻技术都是基于二维平面的加工方式,三维结构获取比较困难,同时可控性较差,但是对于纳米压印技术,只要制作成模板,就可以批量生产三维产品。

这些优势,都让纳米压印技术被推到「最有可能替代 EUV 的下一代光刻技术」的地位。

日本企业是该路线的主要推动者

1995 年,华裔科学家周郁(Stephen Chou)教授首次提出纳米压印概念,从此揭开了纳米压印制造技术的研究序幕。

日本企业将其视为实现逆袭的第一步。毕竟,当年日本尼康、佳能在光刻市场一度称王称霸。由于对未来预判的失误,当 ASML 和台积电共同研发的浸没式光刻机诞生,就将固执的尼康远远甩在身后。从当前光刻机市场占比来看,全球的市场 ASML 占 80%,一家独大,剩下市场基本由佳能、尼康瓜分,市占率分别为 10%、8%。

目前来看,日本在纳米压印技术方面,无论是研发还是产品实现都走在了世界的前列。

佳能自 2004 年开始秘密研发纳米压印技术。2014 年,佳能收购了美国的一家纳米压印技术的研发公司,随后还和东芝一起合作,开始研发纳米压印技术。

2017 年起,铠侠 (KIOXIA)、佳能和大日本印刷 3 家日本企业就在铠侠的四日市工厂(三重县四日市)启动了纳米压印的试制设备的运行。

到了 2021 年,三家企业在技术层面拿出了推向实用化的时间表,计划最早将在 2025 年使如同盖章一样形成电路的「纳米压印」实现实用化。不过现在看来,佳能提前了两年,在 2023 年时就已经推出了纳米压印半导体制造设备。

纳米压印半导体制造设备「FPA-1200NZ2C」

尽管纳米压印技术被吹的神乎其神,但作为一种探索性技术,纳米压印依然存在问题。

一个是前文提到的,制作过程由「非接触」变为了「接触」,这就带来了新的问题。压印过程中,晶片和掩膜之间会进入空气。这有点像手机贴膜,如果在贴膜的过程中混入了空气,那就会有不贴合的情况,这就不能正确地制作电子回路图形了。而在实际的生产过程中,除了空气,细小的粉尘颗粒同样会影响成品良率。

再一个挑战是对准,特别是在晶圆边缘附近。之前是使用相较于实际电子回路四倍大的模子,然后利用透镜其缩小后曝光印制在晶片上。纳米压印的方式则是直接按压模子,所以模子与电子回路是等倍大小,那么精度要求就提高了四倍。

最后,接触压印就需要考虑材料、应力、形变等等问题。作为一套新的方法论,纳米压印光刻还需要大量的研发和市场试错。

纳米压印市场正在逐渐壮大

聊了这么多,我们再来看看纳米压印的实际市场。

在芯片领域,纳米压印可以制造各种集成电路,并且更加擅长制造 3D NAND、DRAM 等存储芯片,与微处理器等逻辑电路相比,存储制造商具有严格的成本限制,且对缺陷要求放宽,纳米压印光刻技术与之非常契合。

从佳能本身的路线图来说,也是按照从 3D NAND 存储芯片开始,逐渐过渡到 DRAM,最终实现 CPU 等逻辑芯片的制造。

存储厂商在芯片制造上对成本把控极为严苛,同时设计的余量可以承受一定的缺陷而不影响成品率,放宽对缺陷的要求,所以目前已经有不少存储厂商计划使用纳米压印技术来制造存储芯片。

大概 SK 海力士是最早开始用这个技术的企业,SK 海力士从佳能引进了纳米压印设备,目前正在进行测试,计划在 2025 年左右使用该设备开始量产 3D NAND 闪存,到目前为止的测试结果良好。据称佳能纳米压印设备的技术指标不错,套刻精度达到了 2.4nm/3.2nm,每小时可制造 100 片以上晶圆,基本达到了 3D NAND 大规模生产的水平。

有业内人士表示:「与 EUV 相比,纳米压印技术形成图案的自由度较低,因此预计将优先用于生产维持一定图案的 NAND 型闪存。」SK 海力士开始采购设备也是因为这个原因。如果纳米压印设备实现商用化,以 SK 海力士为首的 NAND 闪存企业将能够提高从 200 层开始的工序难度越来越高的 3D NAND 闪存领域的生产效率。

铠侠和佳能先前就一起合作研发纳米压印技术,铠侠的目标是将纳米压印技术引入自己的闪存生产线。将来,在新涉足比 15 纳米更加微细的半导体之际,有可能充分加以利用。

总而言之,想要替代「EUV 光刻机」,纳米压印还有一段距离。但是对于业界来说,纳米压印仍是一个可以期待的「备胎」。

评论