盘点用了三星14nm FinFET 制程的产品

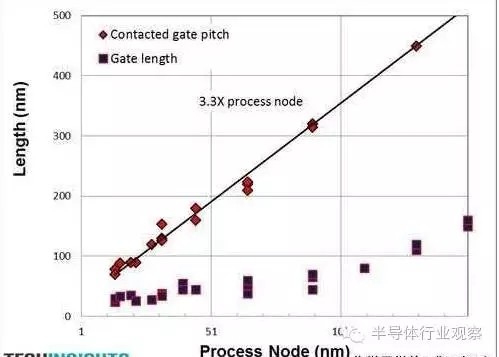

图6提供了一个线索。透过图6分别描绘出针对几个先进逻辑元件所测得的实体层闸极长度、制造商所宣称的制程节点,以及晶体管的接触闸间距。晶体管以130nm节点进行制造时,较大的闸极长度更接近制程节点。但从110nm到65nm,闸极长度微缩的速度较制程节点更快速,也比制程节点更短。至于45 nm及其更小的制程,闸极长度的微缩速率则减缓。

本文引用地址:https://www.eepw.com.cn/article/201610/311948.htm我们还为相同的元件绘制出接触闸间距,这一间距长度是制程节点的3.3倍,而且所有的制程节点在这一点上都是一样的。我们还发现最小的金属间距也可扩展到大约3倍的制程节点。

我们经常使用接触闸间距和6T SRAM单元面积来代表制程节点;但这导致了一个问题:所谓的16nm或14nm制程节点真的是这样的节点尺寸吗?例如,三星的鳍片间距、闸极长度、接触闸间距以及6T SRAM单元面积,都比英特尔的14nm更大,其6T SRAM单元面积也比台积电的16nm SRAM更大。那么,它究竟是不是真的14nm制程?

我们之中有一名工程师认为,鳍片间距最接近于制程节点,就像我们在DRAM中看到的主动间距以及在NAND快闪记忆体中的STI间距一样。我们在表1中列出了英特尔、三星与台积电16/14nm元件的1/3鳍间距,这看起来的确更能代表制程节点。

图6:晶体管闸极长度、接触闸间距与制程节点的比较

那么,我们应该可期待三星新一代的LPP制程有些什么变化?三星在最近的新闻发布中提到LPP制程将可提高15%的晶体管开关速度,同时降低15%的功耗。这些都是透过增加晶体管的鳍片高度以及增强应变工程而实现的。而我则预期还会有一点点的制程微缩,从而使其晶体管尺寸与6T SRAM单元面积更接近于英特尔的14nm制程节点。

评论