英特尔研发周期放缓 或被台积电超过

虽然目前还不知道Ice Lake的更多消息,但先前的报道显示,Intel将把Haswell中的FIVR(全集成式电压调节模块)重新置入其中。

本文引用地址:https://www.eepw.com.cn/article/201601/286316.htm理论上,虽然内置FIVR会增加部分芯片面积,但对电压的控制会更加精确,从而实现更加省电,但这一点在Haswell上却并没有得到体现——由于加入了FIVR,TDP(热设计功耗)非但没有下降,反而从前代的77W进一步增加到了84W。

但Intel显然并没有对FIVR技术完全死心,看来Intel很有可能会把成熟的FIVR技术重新引入到10nm级芯片中。

在10nm工艺节点上,Tiger Lake架构将成为Intel的第二次“Tock”。“Tiger Lake”这一代号虽然在此前的报道中从未被提及过,但这表明了Intel在10nm的工艺节点上也将沿用三代。

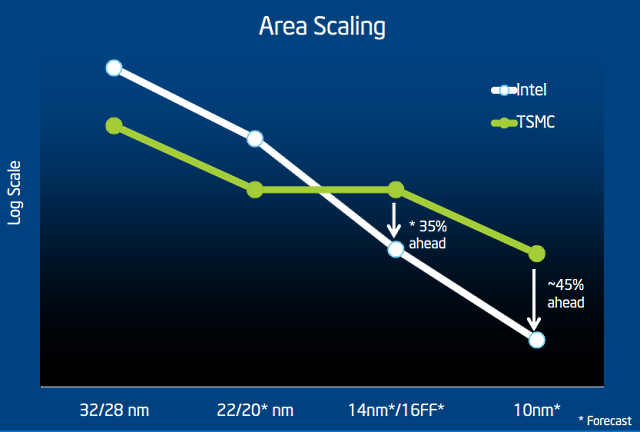

Tick-Tock或将面临台积电的技术挑战

但是,如果Intel真的要按照这个发展战略来不紧不慢地提升自己的技术,那么台积电“在2017年达到7nm技术节点,2020年达到5nm的技术节点”的战略规划显然要比Intel来的更为乐观。

“台积电预计将在2018年上半年开始生产7nm制程的芯片,不仅如此,我们在极紫外光刻技术(EUV)上已经取得了重大突破,很可能会在5nm工艺制程上应用。”

——台积电联席CEO刘德

而Intel官方则表示,如果在5nm节点上硅仍然是一个可行的微处理器材料,那么Intel将于2020年开始研发5nm制程的芯片,我们最早将在2022年才能见到这一芯片。

不过,此前业内的诸多人士都表示硅不会成为5nm级芯片上最具成本效益的材料,并且目前也已经有诸多有望代替硅成为新一代芯片原材料的物质,如碳纳米管等。所以Intel的这个前提有些耐人寻味。

评论