OV5017图像传感器芯片的性能介绍及其应用

本文引用地址:https://www.eepw.com.cn/article/171726.htm

地址号1110与1111的寄存器保留,用于测试。

2.3 数字图像的输出

OV5017中数字视频流的输出必须通过对芯片内视频数据端口,即地址号为10xx的寄存器的读取来实现。其步骤为:

(1)设置地址总线A[3..0]为10xx;

(2)使能片选CSB与输出使能OEB。

若需输出局部图像则应事先设置窗口控制寄存器。

数字视频流输出的时序如图2所示。图中,

TPHD:TCLK下降沿至HREF有效,最大25ns;

TPDD:PCLK上升沿至视频数据有效,最大25ns;

VD:视频数据。

因篇幅所限,这里仅给出图像一行中4个像素输出的时序。根据图2所示时序,外部电路就可以读取芯片输出的图像数据。

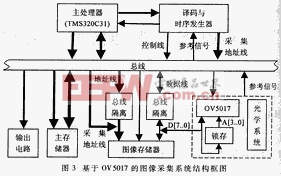

3 基于OV5017的图像采集系统

基于OV5017的图像采集系统结构如图3所示。

在本系统中,OV5017作为系统的图像传感器,其内部将获取的图像采集量化,在外部逻辑的控制下输出数字图像,存入图像存储器。这里,OV5017的管脚A[3..0]与D[3..0]复用共同的外部数据线,因此加一个锁存器将它们分开。在读写OV5017的内部寄存器时,需分两个操作进行,即先选择寄存器,再读定该寄存器。同时,为避免总线冲突,TMS320C31的低8位数据线与OV5017的数据之间和TMS320C31的地址线与采集地址之间各加了一个总线隔离。

系统读取图像的过程为:

(1)对译码与时序发生器初始化;

(2)视需要设置OV5017的内部控制寄存器,如曝光控制、增益控制、窗口控制等;

(3)选择OV5017的视频数据端口,即寄存器10xx;

(4)TMS320C31向译码与时序发生器发信号,通知开始采集图像;

(5)译码与时序发生器使能总线隔离,并根据OV5017输出的参考信号,即VSYNC、HREF与PCLK,生成图像存储器的片选、写及地址信号。这样数字图像即以连续的方式存入图像存储器中;

(6)TMS320C31向译码与时序发生器发信号,通知停止采集图像,OV5017则停止输出数字图像。

在图像采集过程中,TMS320C31可访问除图像存储器与OV5017以外的其他存储器或端口。

该系统由于省略了A/D等器件,因而具有结构简单、体积小、功耗低等优点。同时,由于OV5017内部嵌入曝光、增益、开窗等控制电路,并且编程方便,这就提高了采集系统在功能上的灵活性。本系统适合于监控、多媒体等应用范围。

评论