基于单片机的高速信号测试接口板的实现

在数字电路设计和调试中,对设计单元电路的性能进行实时测试是必不可少的环节。很多情况下,需要通过计算机的比较和分析,来测试设计的电路的性能是否达到要求。这就需要设计一个测试接口板,将计算机产生的测试数据送入单元电路,再将单元电路的输出结果送回计算机。

本文引用地址:https://www.eepw.com.cn/article/171724.htm在电路测试接口板的设计过程中,常常会遇到总线时钟频率较高(如40 MHz以上)、总线宽度较宽(如36 b)、要求测试的数据量较大(几Mb/s)的单元电路。这时实时地进行数据的双向传输比较困难,因为不论采用总线频率较高的PCI数据总线或USB总线[1],都达不到系统要求的数据传输速率,所以必须进行数据的缓存。考虑到PCI总线和USB总线的接口电路复杂、开发周期长,本文介绍一种采用单片机为控制单元,通过RS232C接口,使用高速FIFO存储器件作为缓冲,在单元电路与计算机之间传输数据的方案。该方案实现简单,开发周期短,完全可以满足对于上述的数字单元电路的测试要求。

这里以测试总线频率40 MHz,数据宽度32 b的单元电路为例,介绍用单片机和FIFO实现的高速信号测试接口板方案,整个测试系统结构如图1所示。

1 系统概述

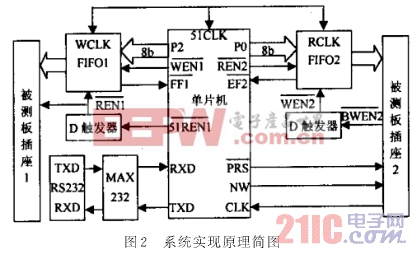

整个系统主要由单片机、FIFO芯片、MAX232芯片以及D触发器芯片构成。图2是系统的原理简图,图中给出 了一些重要的器件和控制信号。

系统的工作流程如下:首先将测试数据从计算机的RS232C口送入单片机,单片机将其变为8 b并行数据写入FIFO1,这期间不对FIFO1进行读操作。FIFO1满后,被测板以40 MHz的总线时钟频率并行读取FIFO1,同时被测板的输出以同样速率写入FIFO2。FIFO2满后,再通过RS232C口将FIFO2中的数据读入PC机,其中的控制操作由单片机及外围电路来完成。下面将分4个步骤介绍系统的工作过程,其中前2个步骤是测试数据从计算机传送到被测板的过程,后面2个步骤描述了被测板的输出结果送回计算机的过程。

1.1 RS232C口与FIFO1的通信(数据从RS232C口输入)

测试数据以串行方式从计算机的RS232C口输出,通过MAX232电平转换后进入单片机的RXD口,再转换为 8 b并行数据从P2口写入到FIFO1。单片机除了控制FIFO1和FIFO2的复位RES(图2中未标出)、FIFO1的写使能WEN1以及FIFO1的写时钟WCLK,还发出一个信号用来辅助读取FIFO1。

由于FIFO1的读取被设置为在数据写入时无效,只有写满了以后才允许被测板读取,因此对于FIFO1满状态的判断及控制非常重要。这里通过计数方式和查询方式同时确定其满状态,方法如下:在单片机内设置一个计数值为256 k的计数器,每送出一个字节,计数器值减1。当计数器减到0,查询FIFO1的管脚的状态,若为低电平,则开启,允许被测板从FIFO1中读出数据,否则向计算机发出错误信号,重新接收数据。

1.2 FIFO1与被测板的通信(数据输入被测板)

FIFO1与被测板的通信连接包括数据线以及读允许REN1。REN1的的作用是控制被测板的读取过程,只有当此信号为低电平,被测板才能从FIFO1中读数据。

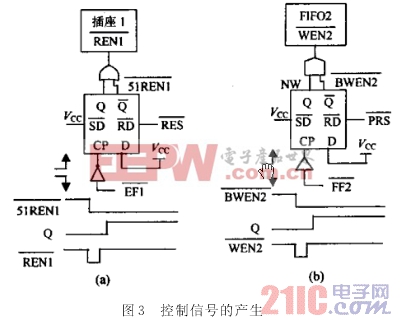

由于被测板的读取速度很高,而单片机的指令周期相对慢得多,当FIFO1被读空后,如果使用单片机来控制读允许使其恢复到高电平,可能在关闭读允许以前被测板已经读入了很多无用数据,所以这里采用FIFO1的空标志位通过D触发器,和单片机的读允许端一起组成控制信号具体电路如图3(a)所示。

评论