利用可配置处理器来创建多标准多分辨率视频引擎

现代的可配置处理器(例如Tensilica的Xtensa处理器)所配的软件工具会自动修改编辑器工具,包括C/C++编辑器、汇编程序、调试器、模仿器和ISS(指令集仿真器)。此时,C编辑器会识别新的C内部指令sub。abs。acc并安排相应的指令,调试器则显示sub。abs。acc功能模块中使用的内部信号,同时,汇编程序会将之作为一个新的指令进行处理,而ISS则对之进行周期精确级仿真。

创建新的加载/存储接口

要在如此之大的寄存器文件(和相应的SIMD功能单元)中读出和写入数据,要求可以进行大规模的加载和存储。还是在可配置处理器中,设计者可以自定义加载和存储指令来直接在自定义寄存器文件中加载和存储数据。接着,编辑器会自动生成对应于这个加载/存储接口的加载/存储指令,从而将数据从内存中加载到寄存器文件中。

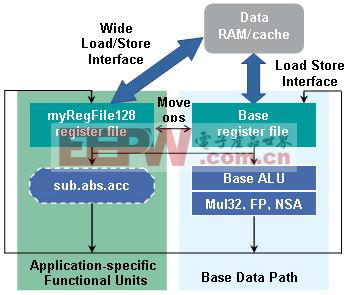

图6是处理器数据路径的更新图。如图中所示,硬件生成工具自动生成大的自定义寄存器文件和加载/存储接口以及所有相关的正向控制和旁路逻辑。特别需要注意的是这些工具还会生成硬件逻辑来将数据从基本寄存器文件转移到用户自定义的寄存器文件中。

图6

加载或存储时更新地址

创建指令来进行自定义加载或存储时,最好能在加载或存储的同时更新地址。这种新的加载/存储指令可以同时进行:

加载A1←存储器(地址1);地址1=地址1+索引更形

这种能够同时进行数据加载/存储和地址更新的指令使得处理器可以进行背靠背加载/存储,而不需要一个中介指令来进行地址更新。

创建FIFO接口和通用IO端口

可配置处理器中另一个重要特征是可以定义FIFO接口和通用IO(GPIO)端口来直接从数据路径中读取和写入数据。这些FIFO接口和GPIO端口的宽度可以是任意的(在这个例子中是1024b),在数字上没有任何限制(例如,FIFO和GPIO端口的宽度都可以是1024)。这些宽的数据路径直接接口可以提供多媒体和网络应用所需的高数据吞吐量,来通过处理器内核读取、处理和写入数据。

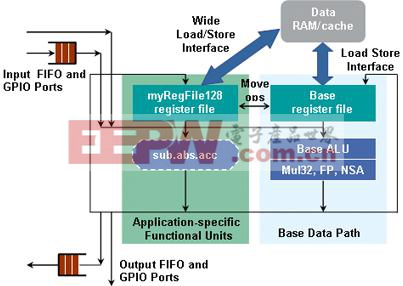

图7显示的是带有这样的FIFO接口和GPIO端口的数据路径。(有了这种方法)我们可以创建一个指令来发射两个FIFO(只要确保这两个不是空的),进行一次复杂的计算(例如循环乘加),并将结果传到另一个输出FIFO上(只要这个FIFO还没有满)。接着,再次由硬件生成工具生成适当的接口信号、控制逻辑和旁路逻辑,并生成已配置处理器所需的完整RTL,同时,软件生成工具则自动生成一套完整的编辑器工具和模仿新指令的周期精确级ISS。

图7:通过FIFO接口和GPIO端口进行的高速通信

加速复杂控制代码

多媒体应用中控制代码的数量和复杂性已经增加到这样的一个程度:它所消耗的计算时间和工作几乎和代码的数据密集型部分一样多。H。26?Mainprofile解码器中的一个关键部分-CABAC算法(内容自适应二进制算术编码)就是这样的一个例子:这种算法几乎就是一棵控制流程判定树,有各种各样复杂的数据计算和比较。

由于CABAC计算过于复杂,很多传统的处理器方案不得不放弃CABAC而选择一个专用的RTL加速器。但是,CABAC可以在可配置处理器上作为一套指令扩展而产生作用,不仅在性能足以媲美RTL方案的性能,同时比起RTL加速器还有另外一个优势,那就是它的数据不需要进出处理器。这样一来就显示出处理器指令扩展的另外一个优势—由于特殊应用硬件位于处理器内部,你可以更好地分割硬件和软件。

总结

现代的可配置及可扩展处理器是创建视频和音频引擎的完美选择,迄今为止已经为众多的半导体ASIC供应商所广泛采用。另外也有一些作为嵌入式SoC模块的视频和音频IP产品。例如,Tensilica公司及其合作伙伴就能供应一套完整的视频和音频IP产品,其中包括XtensaHiFi2音频引擎和一系列多标准多分辨率视频方案,以及H。26?(基本类、主流类和高级类)、MPEG-4(SPandASP)、MPEG-2、VC-1/WM9及各种标准的编码器和解码器软件(编解码器)。这些视频方案覆盖了QCIF、CIF和SD,都以实现HD分辨率为目标,并以低功耗和小封装为设计起点。

由于消费者的需求扩展了消费类设备中ASIC的技术规格要求,越来越多的应用将通过使用可配置处理器来执行。借助于可配置处理器所带来的自动设计流程,新的功能支持将会像软件升级一样简单,而设计和验证时间也将大大降低。

评论