先进封装再进化! 解析NVIDIA GR150导入「CoWoP」的真正意义

AI与高效运算(HPC)进入爆发增长时代,芯片制程、摩尔定律推进趋缓,然而先进封装技术已成为提升整体算力的关键战场。

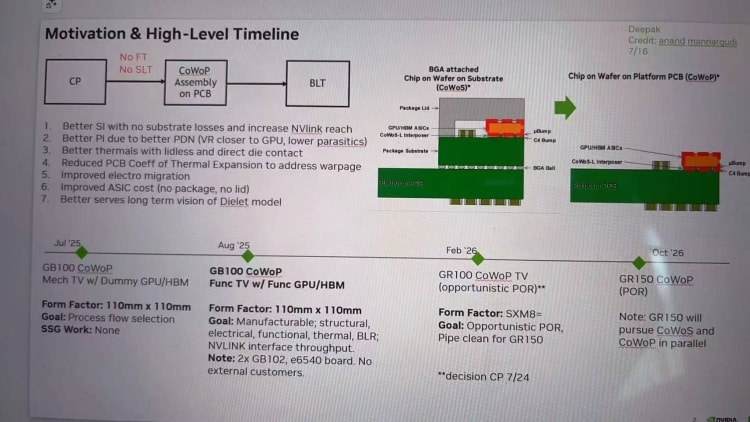

近期,市场流传一份NVIDIA与供应链研发导入「CoWoP」的技术蓝图,这当中有什么值得观察之处? 以下为进一步的分析解读。

从CoWoS到CoWoP 减去封装基板受瞩

近期业界流传一份名为「CoWoP」的全新封装架构,亦即「Chip-on-Wafer-on-Platform PCB」的技术蓝图,据悉,为现有CoWoS的技术演进。

供应链业者透露,「CoWoP=CoWoS-基板」,据该资料显示,CoWoP预计2026年10月在NVIDIA的GR150(Rubin)平台上实现,将是CoWoS与CoWoP「并行」的先进封装策略。

台积电、NVIDIA将与日月光集团旗下的矽品、PCB、设备等供应链,预计2025年9月后,再研议讨论450mmx450mm的可行性设计。

供应链业者表示,目前台积电CoWoS(Chip-on-Wafer-on-Substrate),已成为特用芯片(ASIC)、NVIDIA H100、H200等更先进AI GPU的标配,其结构涵盖芯片(GPU + HBM)、硅中间层(interposer)、封装基板(Package Substrate),最终再以BGA方式焊接到服务器主板。

而据悉,CoWoP技术,简单来说,就是「CoWoS减去封装基板」。 也就是将芯片与中间层组合后,直接安装在强化设计的主板(Platform PCB)上,跳过传统的封装基板与BGA步骤,主板需直接承担高精度讯号与电源布线的功能。

这项删减封装基板一事看似容易,但在技术层面上则难度相当高。

NVIDIA企图再建构护城河 CoWoP带来七大改变

供应链业者表示,NVIDIA正计划透过CoWoP,将原本集中于芯片制程的性能瓶颈,转移至封装与系统级互连,以此建立新的技术护城河。

整体而言,目标就是透过高度系统整合与平台定义权,主导未来AI芯片的标准。

据供应链流传的技术蓝图分析,CoWoP未来可带来「七大改变」,包括:

一、讯号完整性(SI)提升:省去一层封装基板,讯号路径更短、更直接,NVLink和HBM通讯损耗显著降低,传输距离可延长。

二、电源完整性(PI)强化:电压调节器可更靠近GPU,减少寄生参数。

三、散热效能提升:取消芯片上盖(lid),芯片直接接触,带来更佳散热效果。

四、降低PCB热膨胀系数,解决翘曲问题。

五、改善电迁移(Electromigration)。

六、降低ASIC成本(无封装、无盖子)。

七、支持更弹性的芯片模块整合方式,迈向无封装架构长期愿景。

CoWoP有四大挑战 载板技术成熟度高

不过,业界人士指出,CoWoP面对的挑战仍不少,包括:

其一,主板技术门槛大幅提高,Platform PCB必须具备封装等级的布线密度、平整度与材料控制。

其二,返修与良率压力剧增,GPU裸晶直接焊接主板,失败即报废,制程容错空间低。

其三,系统协同设计更复杂,增加开发成本。

其四,技术转移成本高。

供应链认为,这一技术若顺利推进,主板转变为芯片的「最后一层封装」,不仅能降低整体成本,更将主导AI硬件平台的定义权。

不过也仍有PCB业者认为,目前载板技术相对成熟,价格合理,CoWoP欲取代传统封装,仍需时间。

尽管如此,目前市场盛传的技术蓝图资料仍显示,CoWoP已在2025年7月,被列入称为GB100的内部测试平台中,预计2026年10月在GR150平台上,实现CoWoS与CoWoP并行封装策略。

业界推估,台积电、NVIDIA将与封测端的矽品、PCB、设备等供应链,在2025年9月供应链论坛后,可望再研议讨论450mmx450mm尺寸可行性设计。

而据DIGITIMES Research初步分析,GB100、GR150等,推估是NVIDIA内部工程测试品,例如用上一世代的Grace CPU,搭配这一代的Rubin GPU平台,或是Blackwell GPU平台,进行先进封装技术的各种研发讨论,并不一定会商品化对外销售,但在Vera CPU新平台整装上阵前,持续进行技术开发。

尽管如此,NVIDIA携手台积电等供应链,多方大胆尝试先进封装的进化可能性,确实是现在进行式。 预计2026年的半导体先进封装技术发展,更为精彩。

评论