千亿美元蛋糕!3D DRAM分食之战悄然开局

从目前公开的DRAM(内存)技术来看,业界认为,3D DRAM是DRAM技术困局的破解方法之一,是未来内存市场的重要发展方向。

本文引用地址:http://www.eepw.com.cn/article/202402/455490.htm3D DRAM与3D NAND是否异曲同工?如何解决尺寸限制等行业技术痛点?大厂布局情况?

如何理解3D DRAM?

DRAM(内存)单元电路是由一个晶体管和一个电容器组成,其中,晶体管负责传输电流,使信息(位)能够被写入或读取,电容器则用于存储位。DRAM广泛应用于现代计算机、显卡、便携式设备和游戏机等需要低成本和高容量内存的数字电子设备。

DRAM开发主要通过减小电路线宽来提高集成度,但随着线宽进入10nm范围,电容器电流泄漏和干扰等物理限制显著增加,为了防止这种情况,业界引入了高介电常数(高K)沉积材料和极紫外(EUV)设备等新材料和设备。但从芯片制造商角度上看,微型化制造10nm或更先进的芯片仍是目前技术研发的巨大挑战。此外,近期尤其是2nm及以下制程的先进制程角逐战异常激烈。

在技术节点不断更新迭代以及芯片整体面积不断缩小的情况下,半导体业界将目光看向NAND的技术演变,为了克服尺寸限制,将晶体管从平面转换为3D架构,以提高单位面积的存储单元数量,由此3D DRAM的架构设想正式面向公众视野。通俗来讲,传统DRAM的结构是晶体管集成在一个平面上,3D DRAM则将晶体管堆叠为n层,从而分散晶体管。业界称,采用3D DRAM结构可以扩大晶体管之间的间隙,减少泄漏电流和干扰等。

从原理上理解,3D DRAM技术打破了内存技术陈旧的范式,它其实是一种将存储单元(Cell)堆叠至逻辑单元上方的新型存储方式,以在单位晶圆面积上实现更高的容量。

从差异性上看,传统的DRAM在读取和写入数据时需要经过复杂的操作流程,而3D DRAM可直接通过垂直堆叠的存储单元读取和写入数据,极大地提高了访问速度。3D DRAM优势不仅在于大容量、数据访问速度快,同时还具有低功耗、高可靠性等特点,满足各种应用场景需要。

从应用领域上看,3D DRAM具备高速度和大容量,将有助于提升高性能计算的效率和性能;3D DRAM因具有小巧体积和大容量的特点,成为移动设备的理想内存解决方案;3D DRAM的大容量和低功耗特性可满足物联网领域实时处理和传输数据的需求。

此外,自ChatGPT开启了AI大浪潮时代,AI应用技术爆火,AI服务器有望成为存储需求长期增长的强劲驱动力。据美光测算,AI服务器中DRAM数量是传统服务器的8倍,NAND是传统的3倍。

业界持续发力3D DRAM

DRAM市场高度集中,目前主要由三星电子、SK海力士和美光科技等厂商主导,值得一提的是,这三家共同占据了DRAM整个市场的93%以上。

据TrendForce集邦咨询研究显示,在2023年第三季度DRAM市场中,三星的市占率为38.9%,居位全球第一、其次是SK海力士(34.3%)、美光科技(22.8%)。

据业界人士预计,3D DRAM市场将在未来几年快速增长,到2028年将达到1000亿美元。

目前,3D DRAM处于早期研发阶段,包括三星等各方正在加入研发战局,竞争激烈,以引领这一快速增长的市场。

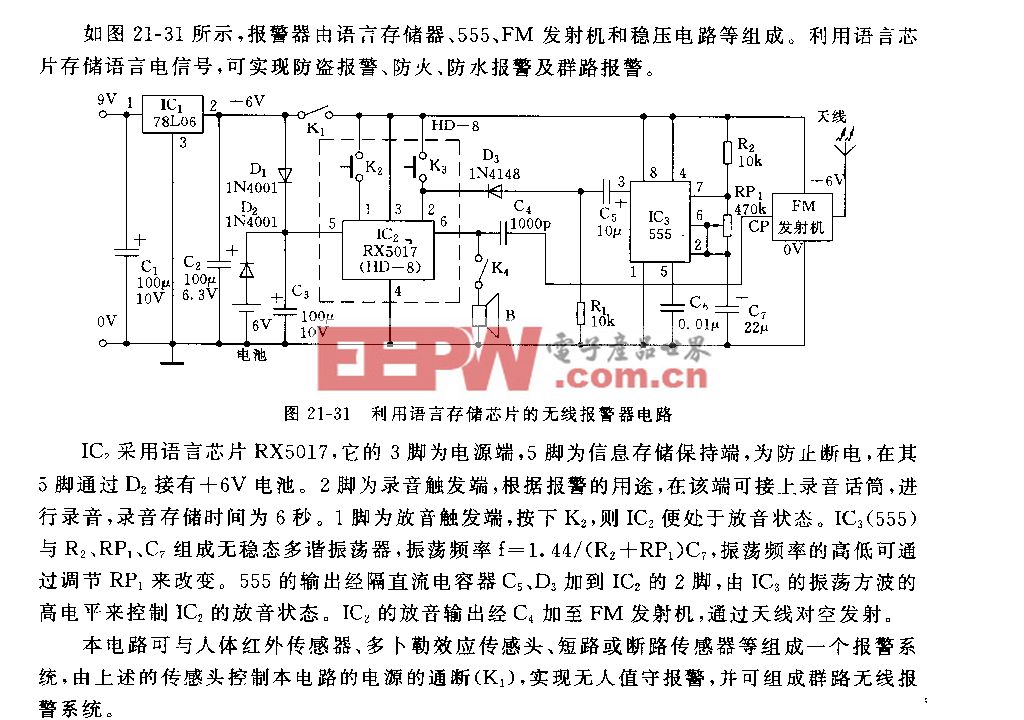

三星:4F2 DRAM

三星从2019年开始了3D DRAM的研究,并在这一年的10月宣布开发出业界首个12层 3D-TSV(硅通孔)技术。2021年,三星在其DS部门内建立了下一代工艺开发研究团队,专注该领域研究。

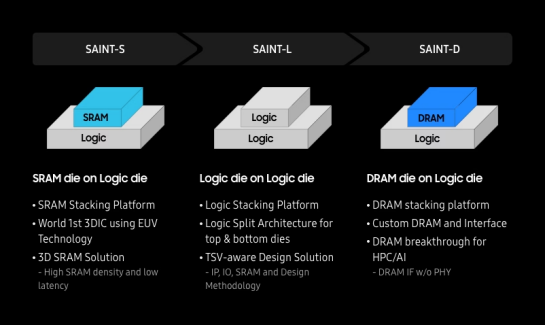

在2022年的SAFE论坛上,三星列出了Samsung Foundry 的整体3DIC历程,并表示将准备用一种逻辑堆栈芯片SAINT-D,来处理DRAM堆叠问题,其设计目的是想将八个HBM3芯片集成到一个巨大的中介层芯片上。

图片来源:三星官网

2023年5月,据《The Elec》引用知情人士消息称,三星电子在其半导体研究中心内组建了一个开发团队,以量产4F2结构DRAM,其目标是将4F2应用于10纳米或以下节点的DRAM制程,因为以目前的技术预计会面临线宽缩减的极限。报道称,如果三星4F2 DRAM存储单元结构研究成功,在不改变节点的情况下,与现有的6F2 DRAM存储单元结构相比,芯片DIE面积可以减少30%左右。

同年10月,三星电子在“内存技术日”活动上宣布,计划在下一代10纳米或更低的DRAM中引入新的3D结构,而不是现有的2D平面结构。该计划旨在克服3D垂直结构缩小芯片面积的限制并提高性能,将一颗芯片的容量增加100G以上。

三星电子去年在日本举行的“VLSI研讨会”上发表了一篇包含3D DRAM研究成果的论文,并展示了作为实际半导体实现的3D DRAM的详细图像。

据《The Economictimes Times》报道,三星电子于近日称已在美国硅谷开设了一个新的R&D研究实验室,专注于下一代3D DRAM芯片的开发。该实验室位于硅谷Device Solutions America(DSA)运营之下,负责监督三星在美国的半导体生产,并致力于开发新一代的DRAM产品。

SK海力士:将IGZO作为3D DRAM的下一代通道材料

SK海力士认为,3D DRAM可以解决带宽和延迟方面的挑战,并已在2021年开始研究。

据韩媒《BusinessKorea》去年报道,SK海力士提出了将IGZO作为3D DRAM的新一代通道材料。

IGZO是由铟、镓、氧化锌组成的金属氧化物材料,大致分为非晶质-IGZO和晶化IGZO(c-IGZO),其中,c-IGZO是一种物理、化学稳定的材料,在半导体工艺过程中可保持均匀的结构,SK海力士研究的正是这种材料。

据业界人士表示,IGZO 的最大优势是其低待机功耗,这种特点适合要求长续航时间的DRAM芯晶体管。通过调节In、Ga、ZnO等三个成分的组成比,很容易实现。

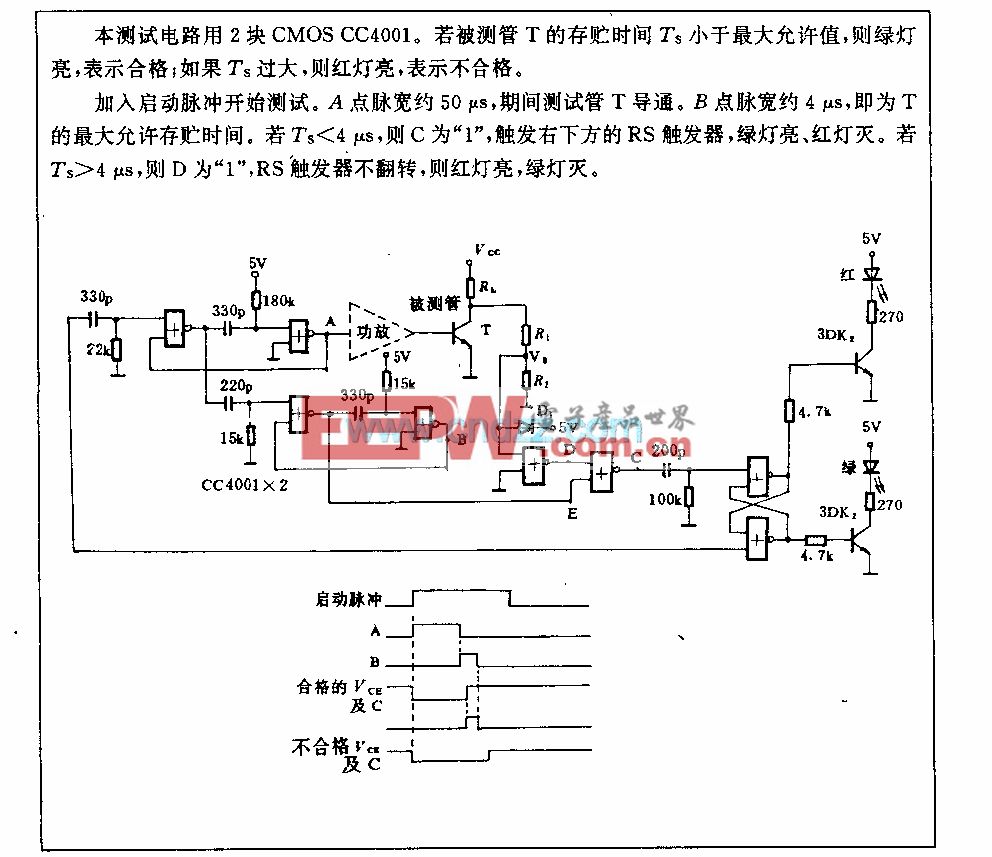

NEO:3D X-DRAM密度可提高8倍

美国存储器技术公司NEO Semiconductor推出其突破性技术 3D X-DRAM,为解决DRAM 容量瓶颈。

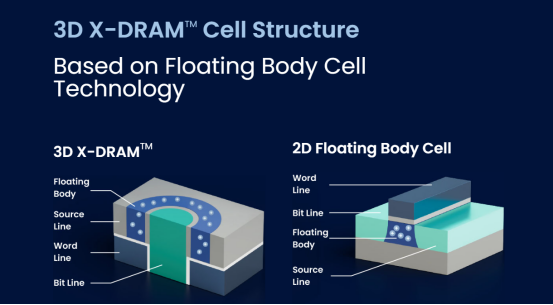

3D X-DRAM是第一个基于无电容器浮体单元(FBC)技术的类似3D NAND的DRAM单元阵列结构。其技术逻辑与3D NAND Flash类似,通过堆叠层数提高存储器容量,类似3D NAND Flash芯片的FBC 技术,增加一层光罩就形成垂直结构,有良率高、成本低、密度大幅提升等优点。

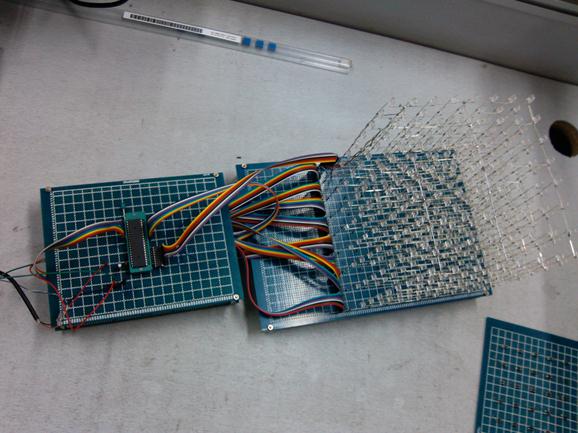

图片来源:NEO Semiconductor官方截图

据 Neo 的估计,3D X-DRAM技术可以实现 230层128 Gb 密度,这是当今 DRAM 密度的 8 倍。NEO提出,每10年容量提升8倍的目标,将在2030到2035年间实现1Tb的容量,较现DRAM核心容量达64倍提升,满足ChatGPT等AI应用对高性能和大容量存储器半导体的增长需求。

NEO联合创始人兼首席执行官Andy Hsu认为,3D X-DRAM将是半导体行业未来绝对的增长动力。

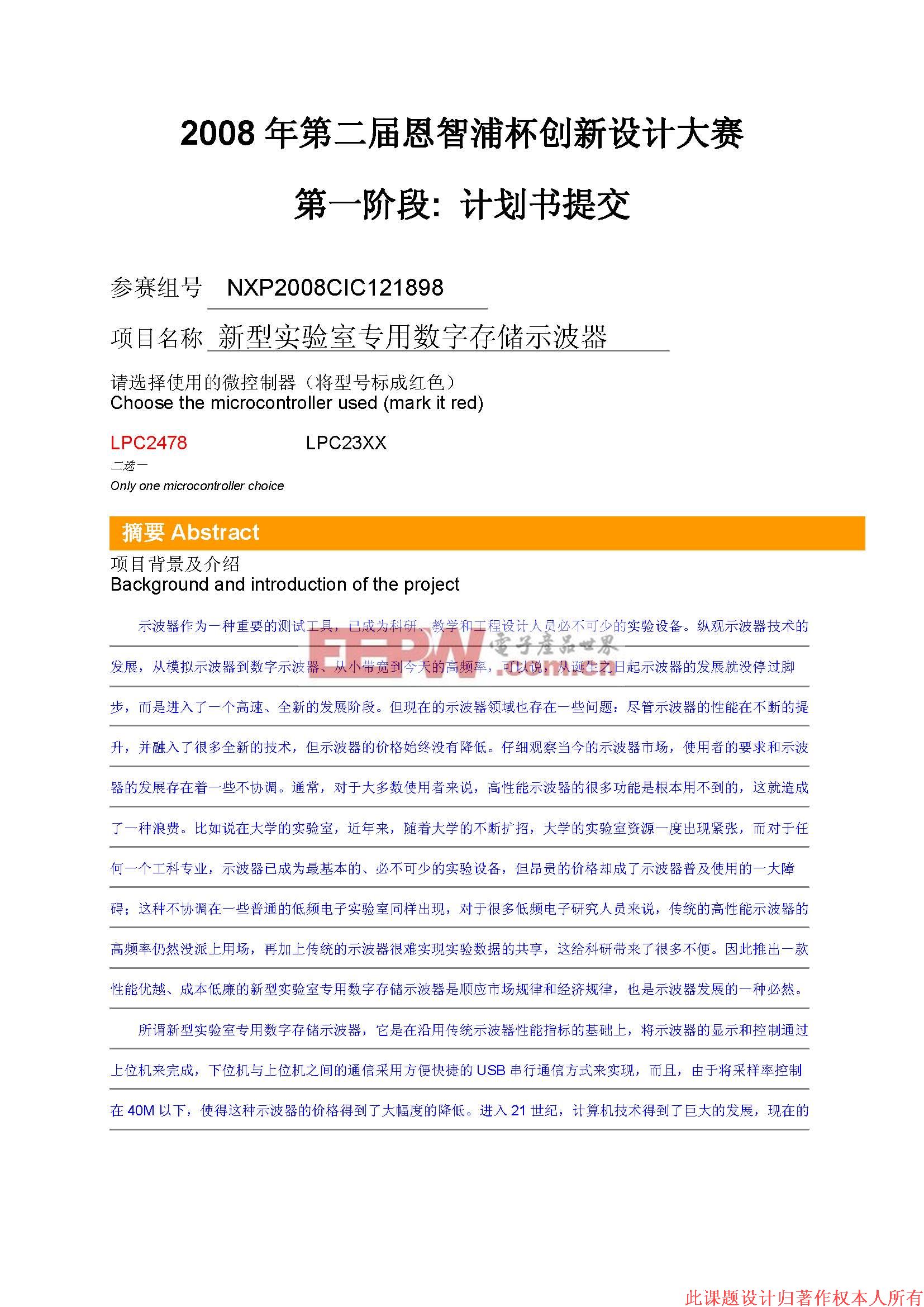

日本研究团队:BBCube 3D,比DDR5高30倍

日本东京理工大学研究团队提出了一种名为BBCube的3D DRAM 堆栈设计技术,该技术可以让处理单元和动态随机存取存储器(DRAM)之间更好地集成。

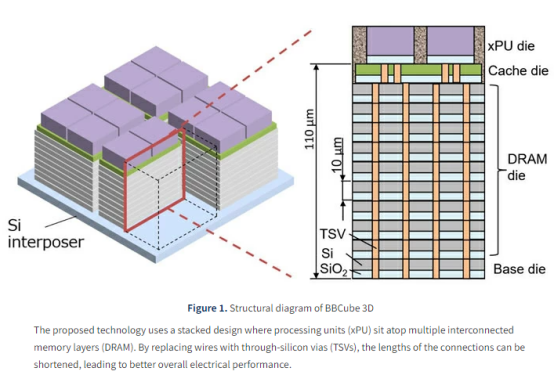

BBCube 3D最显著的方面是实现了处理单元和DRAM之间的三维而非二维连接。该团队使用创新的堆叠结构,其中处理器管芯位于多层DRAM之上,所有组件通过硅通孔(TSV)互连。

BBCube 3D 的整体结构紧凑、没有典型的焊料微凸块以及使用 TSV 代替较长的电线,共同有助于实现低寄生电容和低电阻,在各方面改善了该器件的电气性能。

图片来源:东京工业大学官方截图

该研究团队评估了新体系结构的速度,并将其与两种最先进的存储器技术(DDR5和HBM2E)进行了比较。研究人员称,BBCube 3D有可能实现每秒1.6兆字节的带宽,比DDR5高30倍,比HBM2E高4倍。

图片来源:东京工业大学官方截图

此外,由于BBCube具有低热阻和低阻抗等特性,3D集成可能出现的热管理和电源问题可得到缓解,新技术在显著提高带宽的同时,比特访问能量分别为DDR5和HBM2E的1/20和1/5。

结语

DRAM技术从1D到2D,再到如今结构各异的3D,为业界贡献了解决行业痛点的多样式方案,不过如何优化和改善制造成本、耐久性和可靠性等仍是业界努力挑战3D DRAM技术的难题。由于开发新材料的困难和物理限制,3D DRAM的商业化还需要一些时间。

从当前研究进度看,目前业界正在进行很多关于3D DRAM结构的研发,该结构还处于早期阶段,据业内人士预测,3D DRAM将在2025年左右开始问世,而实际量产在2030年后成为可能。

评论