3D DRAM时代即将到来,泛林集团这样构想3D DRAM的未来架构

动态随机存取存储器 (DRAM) 是一种集成电路,目前广泛应用于需要低成本和高容量内存的数字电子设备,如现代计算机、显卡、便携式设备和游戏机。

本文引用地址:https://www.eepw.com.cn/article/202308/449353.htm

技术进步驱动了DRAM的微缩,随着技术在节点间迭代,芯片整体面积不断缩小。DRAM也紧随NAND的步伐,向三维发展,以提高单位面积的存储单元数量。(NAND指“NOT AND”,意为进行与非逻辑运算的电路单元。)

l 这一趋势有利于整个行业的发展,因为它能推动存储器技术的突破,而且每平方微米存储单元数量的增加意味着生产成本的降低。

l DRAM技术的不断微缩正推动向使用水平电容器堆叠的三维器件结构的发展。

行业由2D DRAM发展到3D DRAM预计需要多长时间?以目前的技术能力来看,需要5到8年。与半导体行业的许多进步一样,下一阶段始于计划。或者说,在DRAM领域,下一阶段始于架构。

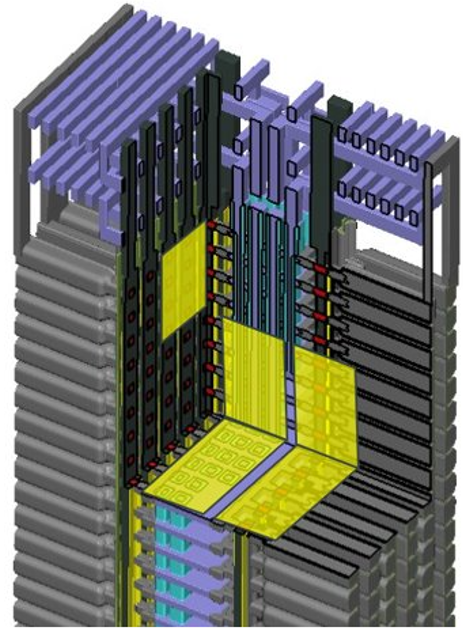

泛林集团正在使用SEMulator3D®计算机仿真软件构想3D DRAM的架构,来探索DRAM的未来。SEMulator3D®计算机仿真软件通常通过模拟实际晶圆制造的过程来虚拟加工半导体器件。以下是我们对3D DRAM架构的设想,涉及六个方面:

l 微缩问题

l 堆叠挑战

l 面积缩小

l 创新连接

l 通孔阵列

l 工艺要求

微缩问题

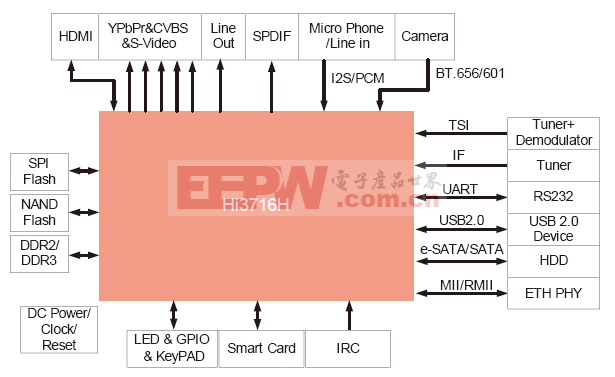

DRAM单元电路由一个晶体管和一个电容器组成。晶体管负责传输电流,使信息(位)能够被写入或读取,而电容器则用于存储位。

DRAM结构由被称为“位线(BL)”的导电材料/结构组成,位线提供注入晶体管的载流子(电流)。晶体管就像一个闸门,可以打开(接通)或关闭(断开),以保持或停止电流在器件内的流动。这种栅极状态由施加在被称为“字线(WL)”的接触导电结构上的电压偏置来定义。如果晶体管导通,电流将流过晶体管到达电容器,并存储在电容器中。

电容器需要有较高的深宽比,这意味着它的高度远大于宽度。在一些早期的DRAM中,电容器的有源区被嵌入到硅衬底中。在最近几代DRAM中,电容器则是在晶体管顶部进行加工。

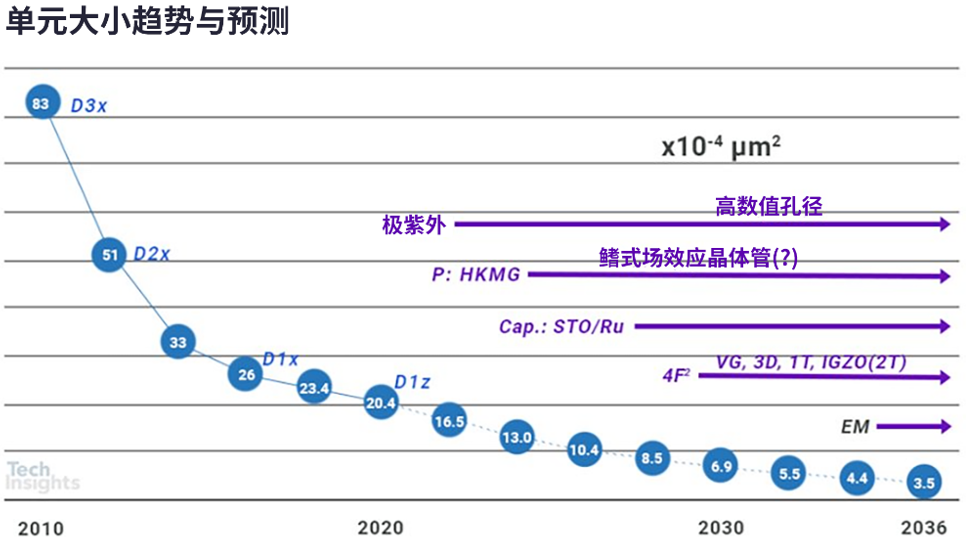

一个区域内可存储的位数或者说单位存储单元的平均面积对微缩至关重要。目前(见上图D1z),每个存储单元的面积约为20.4E-4µm2。很快,通过增高电容器减小面积以提高位密度(即进一步减小单位存储单元面积)的方法将变得不可行,因为用于电容器制造的刻蚀和沉积工艺无法处理极端(高)的深宽比。

上图显示,半导体行业预计能够在单位存储单元面积达到约10.4E-4µm2前(也就是大约5年后)维持2D DRAM架构。之后,空间不足将成为问题,这很可能提升对垂直架构也就是3D DRAM的需求。

堆叠挑战

为了推进DRAM微缩,很自然地需要将2D DRAM组件侧放并堆叠起来。但这面临几个难题:

l 水平方向需要横向刻蚀,但由于凹槽尺寸差异很大,横向刻蚀非常困难。

l 在堆栈刻蚀和填充工艺中需要使用不同的材料,这给制造带来了困难。

l 连接不同3D组件时存在集成难题。

l

最后,为了让这一方案更具竞争力,需要缩短电容器(Cap)的长度(电容器的长度不能和高度一样)并进行堆叠,以提升单位面积的存储单元数量。

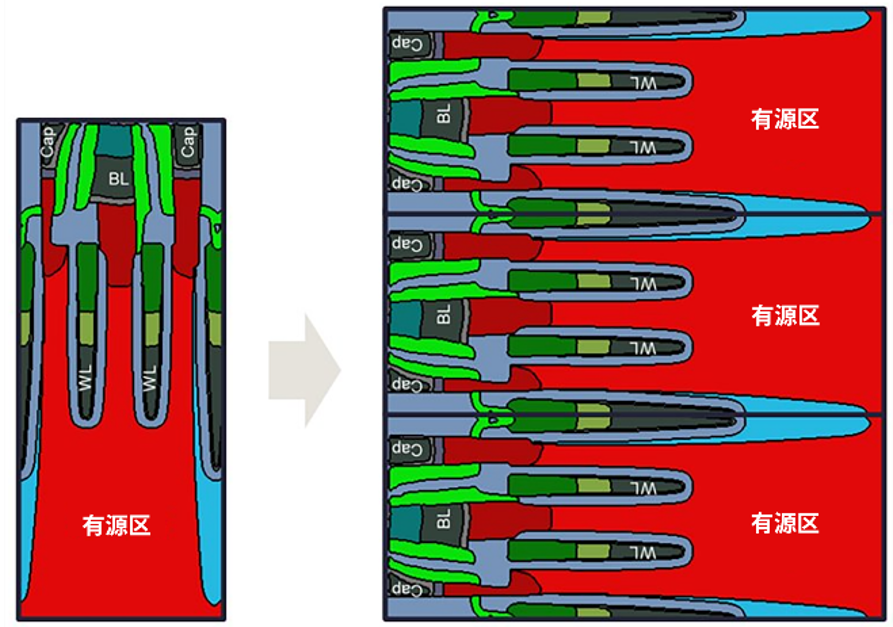

2D DRAM架构垂直定向视图(左图)。将其翻转并将结构堆叠在一起(右图)的做法不可行的主要原因是需要刻蚀横向空腔,并将其以不同的横向深度填充到硅有源区中。

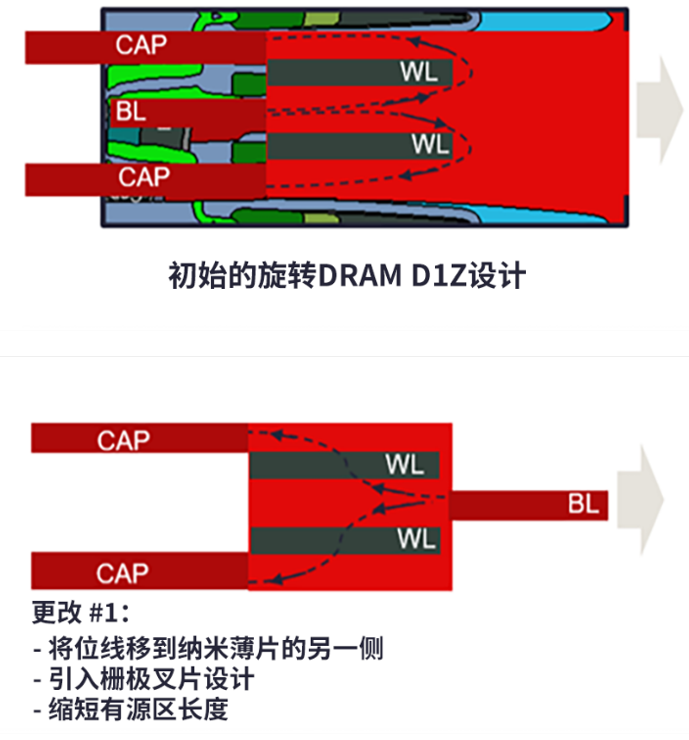

想象一下,上图表示的结构不变,将其顺时针旋转90度,结构将处于自上而下的视图中。在这个方向上,可以堆叠纳米薄片。但同样,这种情况下,原始设计显示的区域非常密集,因此位线和电容器需要自上而下地进行工艺处理,并且距离很近。要实现这种方向的堆叠 (3D),需要重新设计架构。

重新构想的架构

我们的团队使用泛林集团SEMulator3D进行了几处更改,在减小硅区域的同时为电容器的工艺处理提供更多空间,从而缩小纳米薄片的面积。

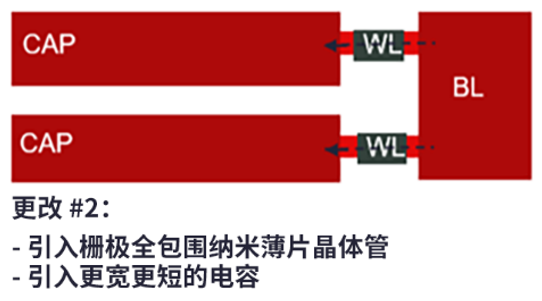

首先,我们将位线移到了纳米薄片的另一侧,使电流通过晶体管栅极穿过整个纳米薄片,这能够从总体上增加电容器工艺处理的空间,并减小硅区域的面积。

其次,我们引入栅极全包围晶体管,以进一步缩小硅有源区。此外,我们还将曾经又窄又高的电容器变得又短又宽。之所以能够做到这一点,是因为把位线移到架构的中心,从而获得了更多空间。

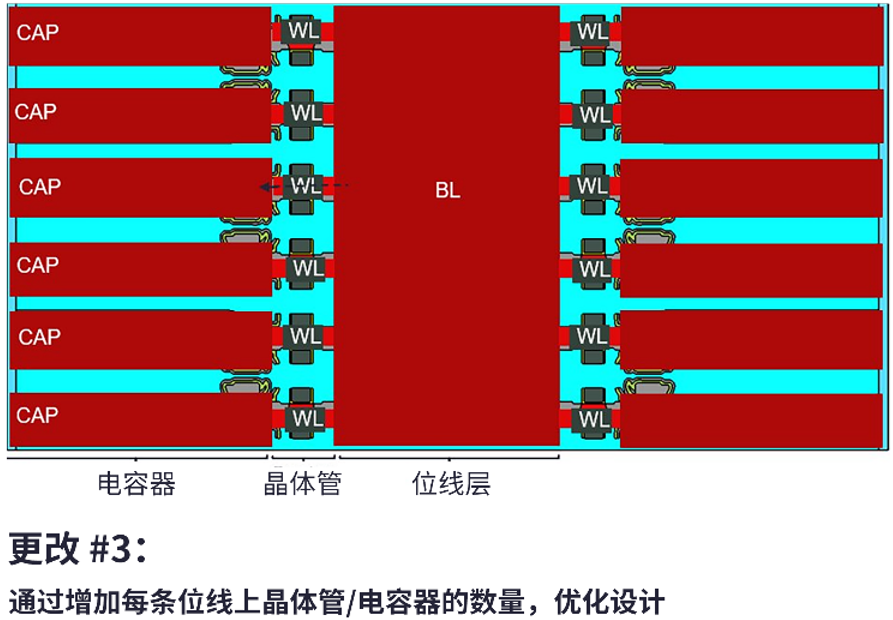

最后,我们通过在位线接触点两侧放置晶体管/电容器的方式增加每个位线接触点的晶体管/电容器数量(没有理由将每条位线的晶体管数量限制在两个以内)。之后,就可以堆叠这种重新配置(如上图自上而下的视图所示)的纳米薄片了。

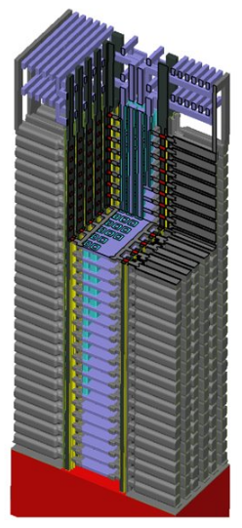

堆叠3D DRAM的第一次迭代有28层高(上图),将比现在的D1z高两个节点(单位存储单元面积约13E-4µm2)。当然,层数越多,位数越多,密度也就越大。

创新连接

3D DRAM的新架构只是一个开始。除了配置之外,还必须就金属化和连接性做出改变。

我们在设计中提出了几种新的方法来促使电流通过中央的位线堆叠,包括连接各层的水平MIM(金属-绝缘层-金属)电容器阵列,以及将栅极包裹在硅晶体管周围(栅极全包围)。其原理是,当电流通过时,只有目标位线(层)被激活。在被激活的层中,电流可以连接到正确的晶体管。

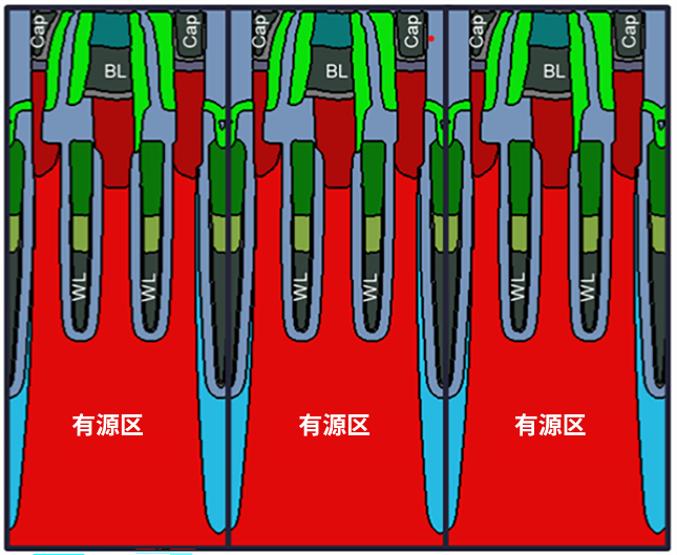

28层3D纳米薄片的关键组件包括:

l 一叠栅极全包围纳米薄片硅晶体管

l 两排晶体管之间的位线层

l 24 个垂直字线

l 位线层和晶体管之间、晶体管和电容器之间的互连

l 水平MIM(金属-绝缘层-金属)电容器阵列

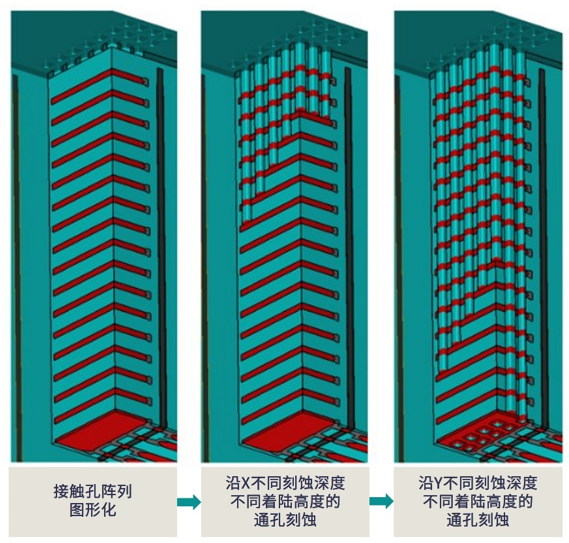

通孔阵列

为了避免3D NAND中使用的台阶式结构的局限性,我们建议引入穿过硅堆栈层且可以在特定层停止(每层一个通孔)的通孔阵列结构,将接触点置于存储单元内部。沟槽制作完成后,我们引入只存在于侧墙的隔离层。

高沟槽用于引入刻蚀介质以去除硅,然后在空沟槽中引入导电金属。其结果是,顶部的每个方格(下面最后三张图片中的浅绿色和紫色方框)只与下面的一层连接。

位线接触图形化

工艺要求

这一虚拟工艺中涉及到的几个模块需要独特且创新的工艺。迄今为止,对于此类路径的探索,变量都是通过物理测试发现和完善的。使用Semulator3D,我们可以实现对这些参数的虚拟优化调整。

我们的实验使工艺要求方面对规格的要求非常严格。刻蚀和沉积专家可能会对我们的模型要求感到震惊:例如,在我们的架构中,需要刻蚀和填充关键尺寸为30nm、深度为2µm的沟槽。

3D DRAM是一种前沿设计,要求采用从未见过或尝试过的工艺和设计,这是从概念走向原型的唯一途径。我们可以进一步推进实验,以了解不同晶圆之间的工艺差异。

未来趋势

3D DRAM技术有望成为推动DRAM微缩的关键因素。单位存储单元面积和电容器尺寸(长度)之间的适当平衡需要通过各种工艺/设计优化来确定,就如上述的这些方案。

通过虚拟加工新架构设计的原型,测试不同存储密度下的不同DRAM设计方案,并为可以帮助制造未经测试器件技术的单位工艺提升规格要求,SEMulator3D可以在制造中发挥重要作用。

这项研究是未来技术评估的起点,有助于确定详细的工艺和设备规格要求、可制造性和良率分析,并因此助力工艺可用性和变异性、技术性能以及面积和成本方面的分析。

相关阅读:

为了实现更小、更快、更节能,芯片制造经历了什么?

评论