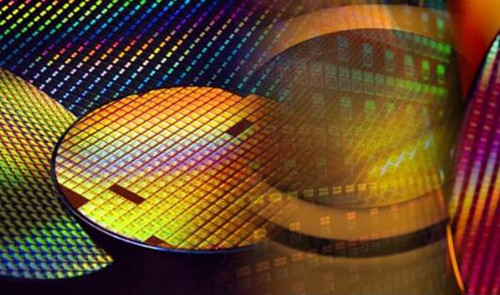

台积电披露3nm工艺更多细节信息 晶体管密度是5nm工艺1.7倍

据国外媒体报道,正如外媒此前所预期的一样,芯片代工商台积电在今日开始的全球技术论坛上,披露了下一代先进工艺3nm的更多细节信息。

本文引用地址:https://www.eepw.com.cn/article/202008/417599.htm

2020年的台积电全球技术论坛,是他们举行的第二十六届全球技术论坛,论坛上分享了第一代5nm、第二代5nm、4nm等先进工艺方面的信息,但在5nm工艺已经投产的情况下,外界最期待的还是5nm之后的下一个全新工艺节点3nm工艺。

在今天的论坛上,台积电也披露了3nm工艺的相关信息。他们的3nm工艺,仍将继续使用鳍式场效应(FinFET)晶体管,不会采用三星计划在3nm工艺节点上使用的环绕式闸极电晶体(GAA)。

同第一代的5nm工艺相比,3nm工艺将使芯片的性能提升10%到15%,能耗降低25%到30%,台积电方面承诺3nm工艺的晶体管密度将是5nm工艺的1.7倍。

外媒在报道中表示,台积电的3nm工艺的晶体管密度,将是第一代的7nm工艺的3倍,可使芯片的能耗降低51%,性能提升32%。

按计划,台积电的 3nm工艺,将在明年进入风险试产,2022年下半年大规模量产。

评论