在40-nm 工艺节点实现世界上最先进的定制逻辑器件

引言

Altera于2008年第二季度推出Stratix® IV和HardCopy® IV器件系列标志着世界上首款40-nm FPGA和业界唯一40-nm ASIC 无风险移植途径的诞生。Altera 通过三年周密的规划和开发,并与代工线合作伙伴台积电(TSMC) 协作,最终获得成功,交付定制逻辑器件展示了无可争议的产品领先优势。Altera 随后于2009 年第一季度发布Arria® II GX 和Stratix IV GT FPGA 系列,实现了业界最全面的收发器系列产品。表1 所示为Altera 开发世界上首款40-nm FPGA 的历史过程。

40-nm 工艺节点非常重要,它为Altera 在性能最好、密度最大、功耗最低、性价比最高FPGA 和HardCopyASIC 上保持领先优势打下了坚实的基础。

40-nm 工艺技术的重要性

40-nm 工艺要比以前包括65-nm 节点和最近的45-nm 节点在内的工艺技术有明显优势。最引人注目的优势之一是其更高的集成度,半导体生产商可以在更小的物理空间中实现更强的功能。国际电子器件大会(IEDM) 报告了密度提高所得到的实际结果,主要的半导体生产商展示了他们在工艺技术上努力的结果。

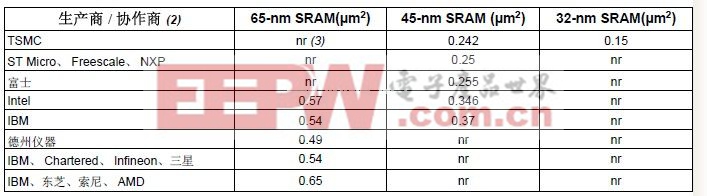

对SRAM 单元大小进行了基准测试,表2 列出了上次IEDM 大会报道的最近工艺节点的SRAM 单元大小(以45-nm 工艺单元大小递增的顺序列出)。如表中所示,工艺技术的提高使半导体生产商能够在更小的面积上实现更强的功能。

注释:

(1) 来源:Real World Technologies, “Process Technology Advancements at IEDM 2007”

(2) 仅列出了报道65-nm 或者45-nm SRAM 单元大小的公司/ 组织

(3) nr = 没有报道

表1. Altera 40-nm 器件的开发过程

日期里程碑

2005 年第一季度Altera 启动40-nm FPGA 和HardCopy ASIC 系列开发,在40-nm 工艺上开始与TSMC 合作。

2005 年第四季度Altera 的第一组9 种40-nm 器件测试芯片投片

2006 年第二季度测试芯片结构评估

2007 年第四季度TSMC 发布产品级45-nm 工艺,加强与Altera 的合作。

2008 年第一季度TSMC 发布40-nm 工艺

2008 年第二季度Altera 发布世界上首款40-nm FPGA, Stratix IV 器件系列和首款40-nm HardCopy IV ASIC。

2009 年第一季度Altera 发布最全面的收发器系列产品,包括Arria II GX 和Stratix IV GT FPGA。

表2. 65-nm 和45-nm 工艺节点报道的最小SRAM 单元 (1)

在40-nm 工艺节点实现世界上最先进的定制逻辑器件Altera 公司

2

40-nm 工艺还具有明显的性能优势。40 nm晶体管逻辑门长度比65 nm 逻辑门长度短38.5%,比45-nm 工艺逻

辑门长度短11%。相应的低阻抗提高了40 nm 的驱动能力,意味着性能更好的晶体管。

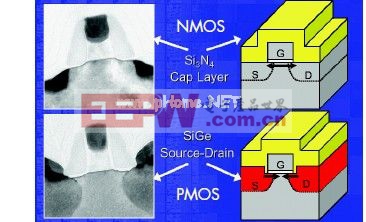

Altera 使用应变硅技术进一步提高了性能。例如, Altera 器件利用了NMOS 晶体管保护层的拉伸应变以及

PMOS 晶体管源极和漏极搀杂硅锗的压缩应变( 参见图1)。这些应变硅技术将电子和空穴的移动能力提高了

30%,使晶体管性能提高了近40%。

图1. 40 nm 应变硅技术实现了性能更好的晶体管

密度和性能的提高意义非常大,而当今系统开发人员面临的最大设计问题之一是功耗。40-nm 节点在这方面也有一定的优势,更小的工艺尺寸减小了产生动态功耗的杂散电容。特别是, TSMC 的40-nm 工艺技术比45-nm 工艺技术有功功率降低了15%。

然而,如果不采取措施,工艺尺寸的减小会增大待机功耗。为解决这些问题以及其他越来越多的功耗问题,Altera 采取了积极的措施来降低40-nm 器件的有功功耗和待机功耗。

结合领先的工艺和器件体系结构满足关键的系统设计需求过渡到40-nm 节点实现了摩尔定律预言的密度和性能优势。利用这些工艺优势并结合器件体系结构创新,Altera 继续为业界提供密度最大、性能最好的定制逻辑器件。由此, Altera® Stratix IV FPGA 和HardCopy IVASIC 分别能够提供650K逻辑单元(LE) 和13M ASIC 逻辑门。在性能方面,Altera 40-nm器件系列逻辑性能达到了600-MHz,收发器性能高达8.5 Gbps,同时, 1.6 Gbps 的LVDS I/O 和1066 Mbps 的单端I/O 性能都是业界最好的,所有这些都不以牺牲信号完整性为代价。

除了最高的密度和最好的性能, Altera 还致力于实现最低的功耗。当今小外形紧凑封装、便携性以及功效的发展趋势推动了对低功耗的需求。产品系统外形非常薄,体积非常小,限制了空气对流、热沉以及其他的散热管理解决方案。此外,很多应用首先考虑的问题是功率元件的工作成本,这促使低功耗成为最明显的竞争优势,是很多应用中必须要考虑的问题。设计目标在这方面的变化使得功耗成为选择系统元件时首先要考虑的标准。

FPGA 供应商的器件在功能越来越强的电路板上发挥的作用也越来越大,在很多情况下要实现系统核心功能,器件功耗管理的难度也随之增大。需要很大的投入才能在提高性能和降低功耗上达到平衡。

评论