采用带有收发器的全系列40-nm FPGA 和ASIC 实现创

人们对宽带服务的带宽要求越来越高,促使芯片供应商使用更多的高速串行收发器。因此,下一代应用采用了多种数据速率,从几Mbps 到数百Gbps,在一种设备中集成了多种协议和服务。以太网等迅速发展的标准以及对提高数据速率的需求使得高速收发器成为主要的性能判定依据。标准单元ASIC 和ASSP 不具有人们需要的灵活性,其成本和风险无法让用户及时实现技术创新。本文介绍带有收发器的全系列40-nmFPGA 和ASIC,发挥前沿技术优势,在前一代创新基础上,解决下一代系统难题。

引言

现代意义上的互联网虽然只经历了十几年的时间,却已经成为技术创新和带宽增长的主要推动力量。更新现有通信系统以及新应用的出现要求采用更大的宽带和更高的数据速率。今天,以视频为主的网络下载和点对点网络连接( 文件共享) 占用了80% 的带宽。流媒体( 视频点播电影和电视)、IP 承载视频和互联网游戏等新应用占用的带宽不到10% 。考虑到这些因素,互联网仍处于发展初期,今后将持续强劲增长。

市场上最近推出的通信设备已经开始向40 甚至100 千兆以太网(GbE) 端口过渡,以更低的成本和功耗,在更紧凑的封装中实现更大的带宽。而且,摩尔定律还在不断推动着半导体行业发展,集成电路上的晶体管数量每两年就会加倍。新一代产品使用45-nm 或者40-nm 工艺来集成更多的功能,提高每一功能的工作性能和逻辑密度,降低功耗,而满足日益增长的带宽需求的关键则是更多、更快的高速串行收发器。

本文介绍高速串行收发器的发展趋势,以及系统规划人员和设计人员所面临的挑战。文章还回顾了某些特殊的市场需求,为满足这些需求,可编程逻辑器件(PLD) 供应商必须提供带有收发器的多种产品组合。这些器件具有丰富的逻辑、特性和I/O 功能,客户利用它们能够开发出满足各种性能、功耗和成本目标的产品。

高速收发器技术的发展趋势提高高速串行收发器的数据速率以及器件中收发器的数量可以实现更大的带宽和更高的数据速率。使用以

下技术可以获得带宽达到100G 的接口:

■ 10 个10.3-Gbps 收发器(CAUI 协议)

■ 20 个6.375-Gbps 收发器(Interlaken 协议)

■ 40 个3.125-Gbps 收发器(XAUI 协议)

■ 100 个1.25-Gbps 收发器(SGMII 协议,注意,这只是用于演示目的,并不实用)

考虑到每个器件所有输入和输出数据通道的两端口需求,如果收发器数据速率不能相应的提高,即使是采用最现代的工艺技术也难以满足收发器的数量要求。

很多系统混合了DSP 模块、控制处理器、ASSP、ASIC 和FPGA。系统规划人员面临的挑战是对系统进行划分,把这些器件连接起来,以满足应用性能和带宽要求。在很多情况下,由于ASSP 和ASIC 技术创新发展较慢,无法实现更快的接口。另一挑战是这些器件所提供的各类协议,规划人员不得不牺牲性能,重新使用原来的接口。这一般通过桥接器件――传统的FPGA,连接原来的协议和新协议。解决这些问题最终会降低系统成本。

带有收发器的数据链路不但支持更高的数据吞吐量,而且功效非常高,进一步提高了系统集成度,成为系统的关键组成部分。串化器/ 解串器(SERDES) 收发器是替代原有并行技术所必须采用的技术。通过使用收

发器技术,设计人员能够解决当今高速数据链路设计中的关键问题:

■ 信号完整性:相对于并行接口,串行接口的延时和偏移都比较低。在串行协议应用,以及驱动背板方面,要求收发器具有优异的信号完整性,较低的抖动和误码率(BER)。

采用带有收发器的全系列40-nm FPGA 和ASIC 实现创新设计Altera 公司

2

■ 复杂的电路板:使用串行接口可以减小电路板面积,减少所使用的电路板元件数量以及电路板层数。例如, PCI Express (PCIe) 接口将引脚和电路板面积减少了50%,而带宽提高了一倍。

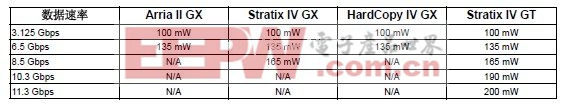

■ 功耗和散热:串行接口的功耗要低于并行接口。例如,Stratix IV GT FPGA 的10G 接口在10.3 Gbps 时的功耗为190 mW, Altera 40-nm 收发器上的收发器 PMA 功率。表1 详细列出了40-nm 工艺节点各种数据速率下的功耗。

总之,系统规划人员面临三种主要挑战:

■ 在提高带宽和数据速率时,需要更多、更快的收发器。

■ 既有原来的高速协议,又有各种不断发展的新标准。

■ 符合背板和协议要求需要有优异的信号完整性。

收发器接口是系统规划人员首先要考虑的关键因素,而器件选择取决于所能够提供的功能、性能、功耗和成本目标。最终,一定的市场需求决定了收发器系列产品最合适的功能。

市场需求

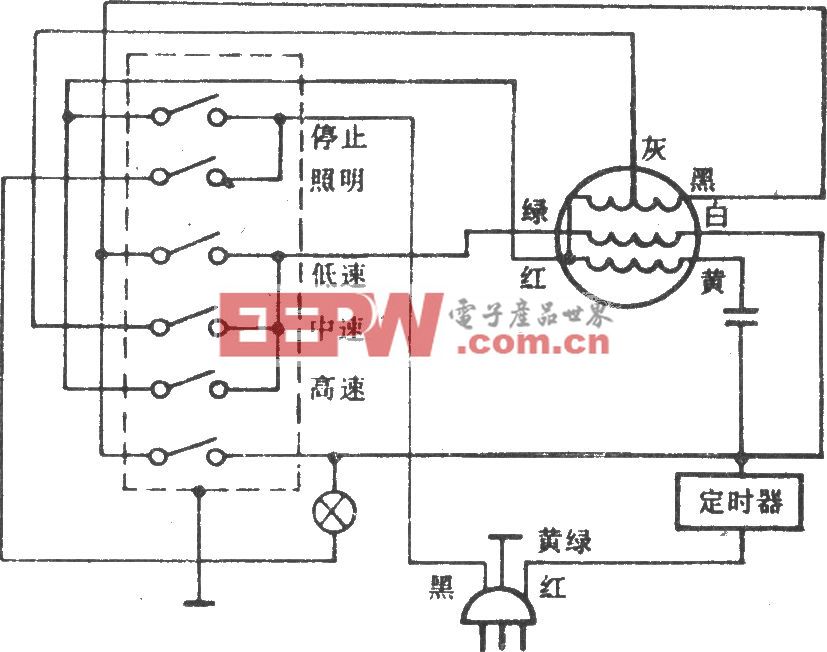

图1 显示了使用以太网协议的几个例子,目前的通信基础设施中使用了收发器。网络中的每一部分都使用

了串行收发器技术,但是有不同的带宽要求。越靠近用户侧,成本和功耗就越敏感,同时,带宽也在降低,

收发器速率和数量也在减少。此外,随着实际应用中处理需求的变化,器件密度和特性的关系也在不断变

化。

图1. 通信基础设施中的收发器

表1. PMA 收发器功耗/ 通道对比

3

固网接入、传输和网络设备

以太网已经发展成为当今应用最广泛的物理层和链路层协议。而作为IEEE 标准802.3ae 于2002 年发布的10GbE 是目前最快的标准, IEEE正在制定40GbE和100GbE 以太网标准。网络已经向数据包传输和全以太网设备过渡,应用范围包括数据包处理和流量管理功能为主的桥接和全数据通道处理等(1)。根据网络中靠近用户的程度以及位置,带宽从10 Gbps 至20 Gbps 发展到 40 Gbps 至80 Gbps,甚至是100 Gbps。并不存在能够满足所有需求的解决方案,因此,设备必须能够支持不同的密度、特性、性能、功耗和成本目标。

关键需求推动了技术创新,包括对集成10G 收发器、高密度和高性能的需求,以及对以太网、GPON、CEI-6/Interlaken 和SONET/SDH 等协议标准的支持。

无线设备

过去,无线标准( 空中接口) 在发展过程中采用了不同的技术和物理通道,但是,对于3.9G/4G,更大的载波带宽(20 MHz) 使得所有主要空中新接口使用OFDMA 技术。虽然正交频分复用多址接入/ 多输入多输出(OFMDA-MIMO) 方法有可能在不久的将来实现技术融合,但目前的标准仍在不断发展,继续得以实施。

主要的无线需求包括在同一系统中对多种标准的支持,新一代体系结构中较强的信号处理能力,减少系统总延时等,所有这些需求都要求进一步提高集成度。而且,无线解决方案必须能够灵活的延伸到名为毫微微基站( 以及微微基站、微基站和宏基站等) 的家庭基站中。这些市场和技术要求推动了高度集成方案的发展,最终成为芯片系统(SoC)。而且,这些收发器PLD 所具有的优点和其他解决方案具有可比性,甚至优于其他方案:

■ 在用户数量或者每单元吞吐量上的成本和性能

■ 每Mbps 和每mm2 功耗和面积

■ 不同空中接口和协议的芯片间、卡对卡以及机箱之间接口高速收发器的灵活性和可更新能力

此外,很难有能够满足所有需求的通用解决方案。推动技术创新的关键需求包括更高的集成度,更低的成本,更好的性能,集成了DSP 功能的信号处理能力,以及支持CPRI/OBSAI 和Serial RapidIO® 等专用协议。

军事、广播、计算机和存储、测试和医疗,以及其他市场领域

其他市场领域对收发器的需求各有不同,需要综合考虑密度、性能、特性和功耗要求。PCIe Gen1 和Gen2以及以太网等标准协议得到了广泛应用。某些市场对协议有特殊的要求,例如,广播应用的SDI,以及计算机和存储的SATA/SAS、HyperTransport 和QPI 等。由于很多应用只需要采用支持专用协议的收发器,因此, 10G 收发器在宽带连接上迅速得到了应用,成为很多产品的主要技术推动力量。

关键技术

带有收发器的FPGA 和ASIC 系列产品采用的技术包括工艺技术、支持可编程功耗技术的功耗和性能优化措施、逻辑架构、I/O、PLL、外部存储器接口、高速串行收发器、时钟数据恢复和时钟产生、预加重和均衡,以及在PCIe 等协议上应用硬核知识产权(IP) 等。

评论