采用带有收发器的全系列40-nm FPGA 和ASIC 实现创

工艺技术和40-nm 的优势和以前的65-nm 节点以及最近的45-nm 节点相比, 40-nm 工艺有很大的优势。最显著的一点是更高的集成度,半导体生产商可以在更小的管芯中集成更多的功能,生产出密度更高的器件。

40-nm 工艺还进一步提高了性能。40 nm 最小的晶体管逻辑门长度比65 nm 逻辑门长度短38.5%,比45-nm 工艺的逻辑门长度短11%。40 nm 的阻抗进一步降低,从而提高了驱动能力,实现了性能更好的晶体管。应变硅技术使电子和空穴的移动能力提高了30%,晶体管性能提高了近40%。

采用带有收发器的全系列40-nm FPGA 和ASIC 实现创新设计Altera 公司

4

虽然密度和性能的提高非常显著,但是,当今系统开发人员在设计中需要着重考虑的是功耗问题。40-nm节点在功耗上也有一定的优势,更小的工艺尺寸减小了导致动态功耗的杂散电容。特别是,台积电(TSMC)的40-nm 工艺技术要比其45-nm 工艺技术的有功功耗低15%。(2)

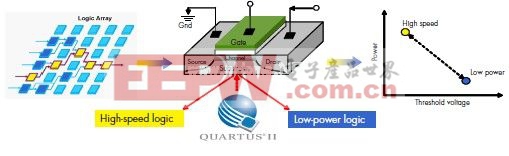

但是,工艺尺寸的降低却增大了待机功耗。Altera 使用多种方法来降低静态功耗,包括多阈值晶体管、长度不同的晶体管沟道、三重氧化等,并且在对性能要求不高的PLD 上综合考虑性能和功耗,例如配置逻辑等。

可编程功耗技术和性能

除了常用的电路设计方法, Altera 还引入了65-nm Stratix® III FPGA 的可编程功耗技术(3) 来降低静态功耗。可编程功耗技术使静态功耗降低了70%,在设计中以最低的功耗实现最好的性能。这一创新技术利用了这一事实――在典型设计中,全部逻辑中只有很少一部分用在关键时序通道上。基准测试表明,时序余度很小的高性能逻辑和时序余度较大的慢速逻辑比平均为30:70。

在任何设计中, Altera 的Quartus® II 开发软件自动确定设计中每一通道的松弛余度。这样,通过调整晶体管的反向偏置电压,将每一逻辑模块、存储器和DSP 模块的晶体管自动设置为合适的模式――高性能或者低功耗:

■ 在低功耗模式中, Quartus II 软件减小反向偏置电压,使晶体管很难接通。这样,减小了时序不重要电路中的亚阈值泄漏电流,以及无用的静态功耗( 图2 中的蓝色部分)。

■ 在高性能模式中, Quartus II 软件增大反向偏置电压,时序关键通路上的晶体管更容易接通,以满足设计中规定的时序约束要求,实现最佳性能( 图2 中的黄色部分)。

图2. Quartus II 软件降低了功耗,提高了性能本文引用地址:http://www.eepw.com.cn/article/191798.htm

逻辑架构和通用I/O

Altera 的40-nm 器件架构使用了包括自适应逻辑模块(ALM)、TriMatrix 片内存储器模块和DSP模块的通用内核逻辑体系结构。ALM 含有一个可配置8 输入分段式查找表(LUT)、两个嵌入式加法器和两个寄存器,并采用了MultiTrack 互联结构进行布线,以支持高速逻辑、算法和寄存器功能,器件利用率非常高。

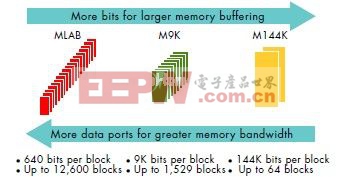

TriMatrix 片内存储器提供三种不同的存储器模块容量,大大提高了效率和灵活性,如图3 所示。

Power

High speed

Low power

Threshold voltage

Source

Substrate

Drain

Channel

Gnd

Gate

High Speed Logic Low Power Logic

High-speed logic Low-power logic

Altera 公司 采用带有收发器的全系列40-nm FPGA 和ASIC 实现创新设计

5

图3. TriMatrix 存储器结构

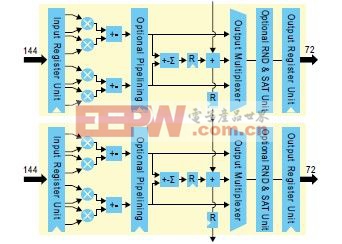

图4 中的DSP 模块是高性能芯片体系结构,其强大的可编程能力可以在多种应用中实现最佳处理功能。每一模块含有8 个18x18 乘法器,以及寄存器、加法器、减法器、累加器和求和单元,这些都是典型DSP 算法中常用的功能。DSP 模块支持可变位宽和各种取整饱和模式,有效地满足了应用需求。

图4. DSP 模块体系结构

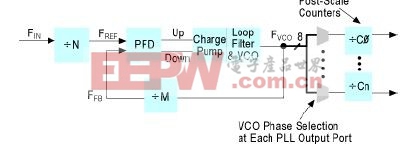

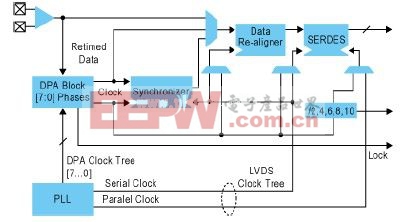

通用PLLAltera 的通用锁相环(PLL) 包括闭环频率控制系统,该系统基于输入时钟信号和受控振荡器反馈时钟信号之间的相位差。图5 显示了PLL 中主要组件的简要结构。

6

图5. PLL 结构图

这些PLL 的模拟特性使其具有非常低的抖动,能够实现可靠的时钟方案。很多可配置时钟输出能够非常灵活的实现系统时钟,为存储器接口和I/O 接口输出时钟。

最佳通用I/O 和外部存储器接口

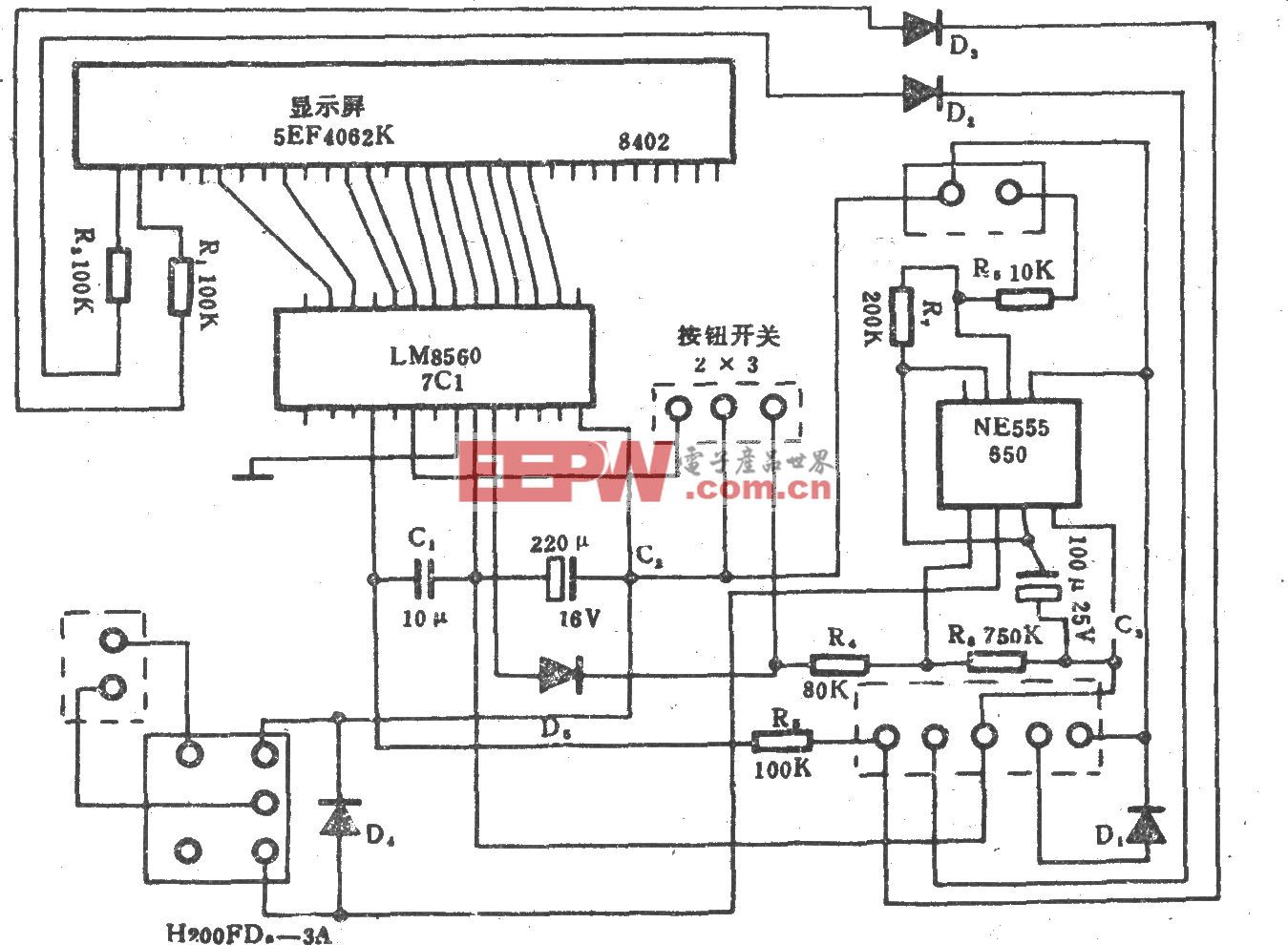

如图6 所示, I/O 结构的关键构建模块包括:

■ 单端I/O 支持,提供可编程摆率和驱动能力,可变延迟链补偿电路板走线,以及串行和并行动态片内匹

配(OCT)。

■ 支持差分片内匹配的高性能LVDS 传输和接收差分信号

■ 为多通道LVDS 接口提供的硬核动态相位对齐(DPA) 模块,避免了时钟至通道和通道至通道偏移,以及

时钟转发功能,实现软核时钟数据恢复(CDR)。

图6. DPA 结构图

Altera 的I/O 引脚支持已有以及新兴的外部存储器标准,例如,DDR、DDR2、DDR3、QDRII、QDRII+ 和RLDRAMII 等。它们包括自校准数据通路,对自己不断进行动态调整,在工艺、电压和温度变化时,提供最可靠的工作频率。其他电路包括对齐和同步、通道去偏移、读/ 写调平,以及时钟域交叉功能等。

评论