采用带有收发器的全系列40-nm FPGA 和ASIC 实现创

高速串行收发器

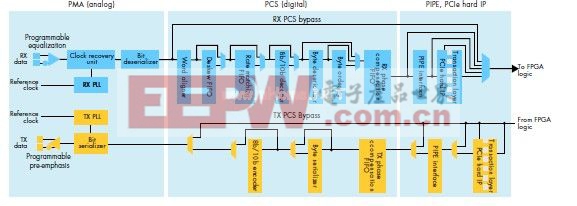

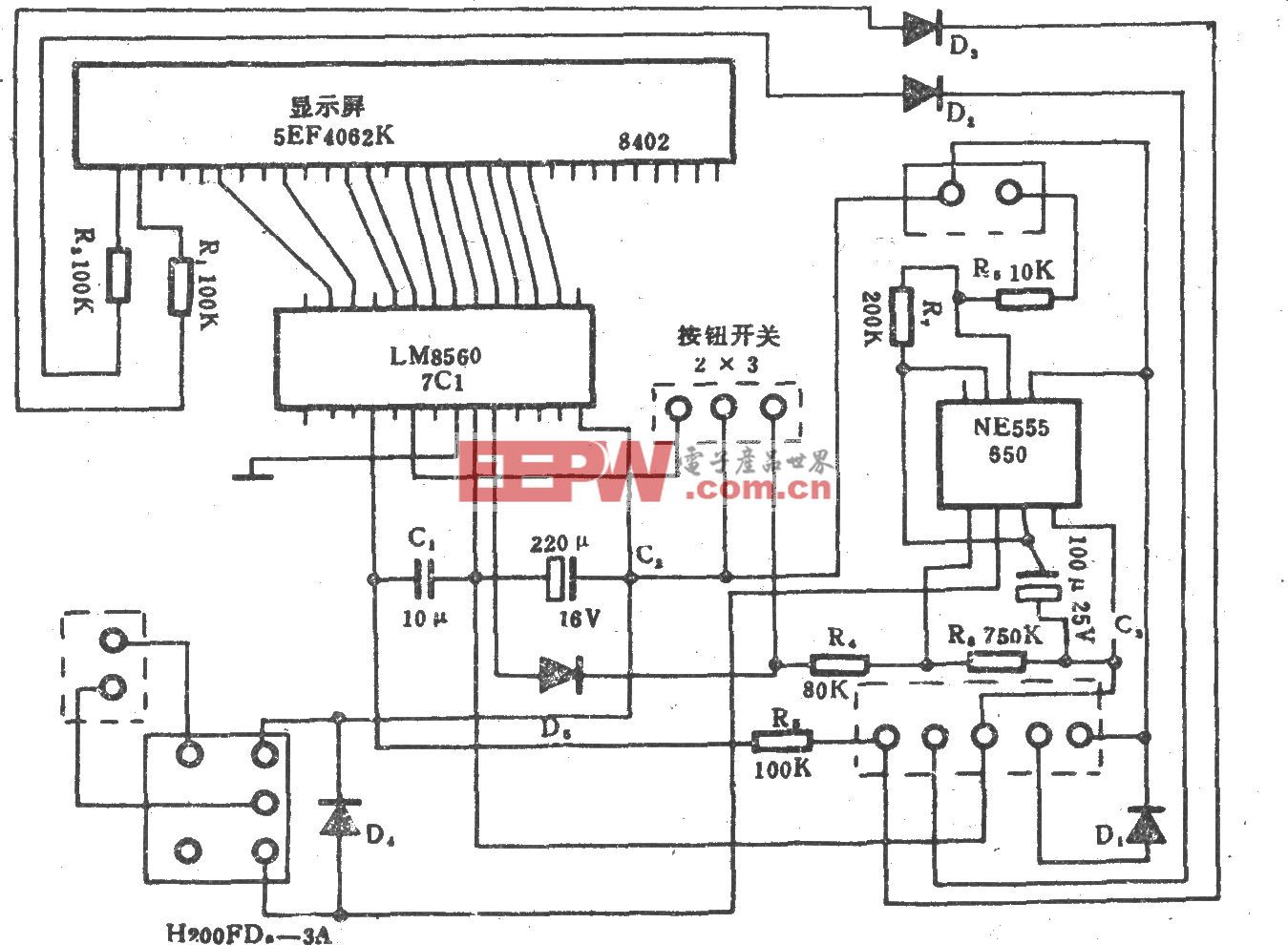

Altera的高速收发器模块在物理介质附加(PMA)和物理编码子层(PCS)使用通用体系结构(图7所示)。 根据设计人员的不同要求,可以旁路PCS 中的模块。

Altera 公司 采用带有收发器的全系列40-nm FPGA 和ASIC 实现创新设计

7

图7. PMA 和PCS 结构图本文引用地址:https://www.eepw.com.cn/article/191798.htm

PMA 功能可以用在模拟电路中,包括:

■ CDR

■ SERDES

■ 可编程预加重和均衡

■ I/O 缓冲,支持动态可控设置( 输出差分电压和差分OCT)。

PCS 提供数字功能以适应背板、芯片至芯片和芯片至模块应用的多种关键协议。这些数字模块为增强对协议的支持而进行了优化,减少了实现物理层协议所需要的器件资源,同时降低了功耗。与特定的IP 和参考设计相结合,这些模块能够提供完整的协议解决方案,缩短了设计周期,降低了风险。PCS 功能的例子包括8b/10b 编码器/ 解码器、相位补偿FIFO 缓冲、字对齐器和速率匹配器,在收发器模块中提供对协议的支持。

此外,还提供专用状态机,支持PCIe、GbE 和XAUI 协议。

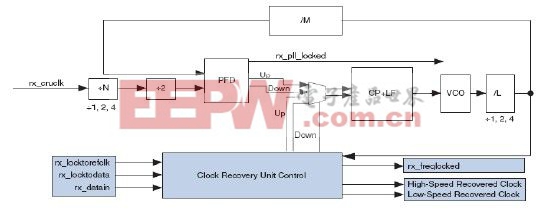

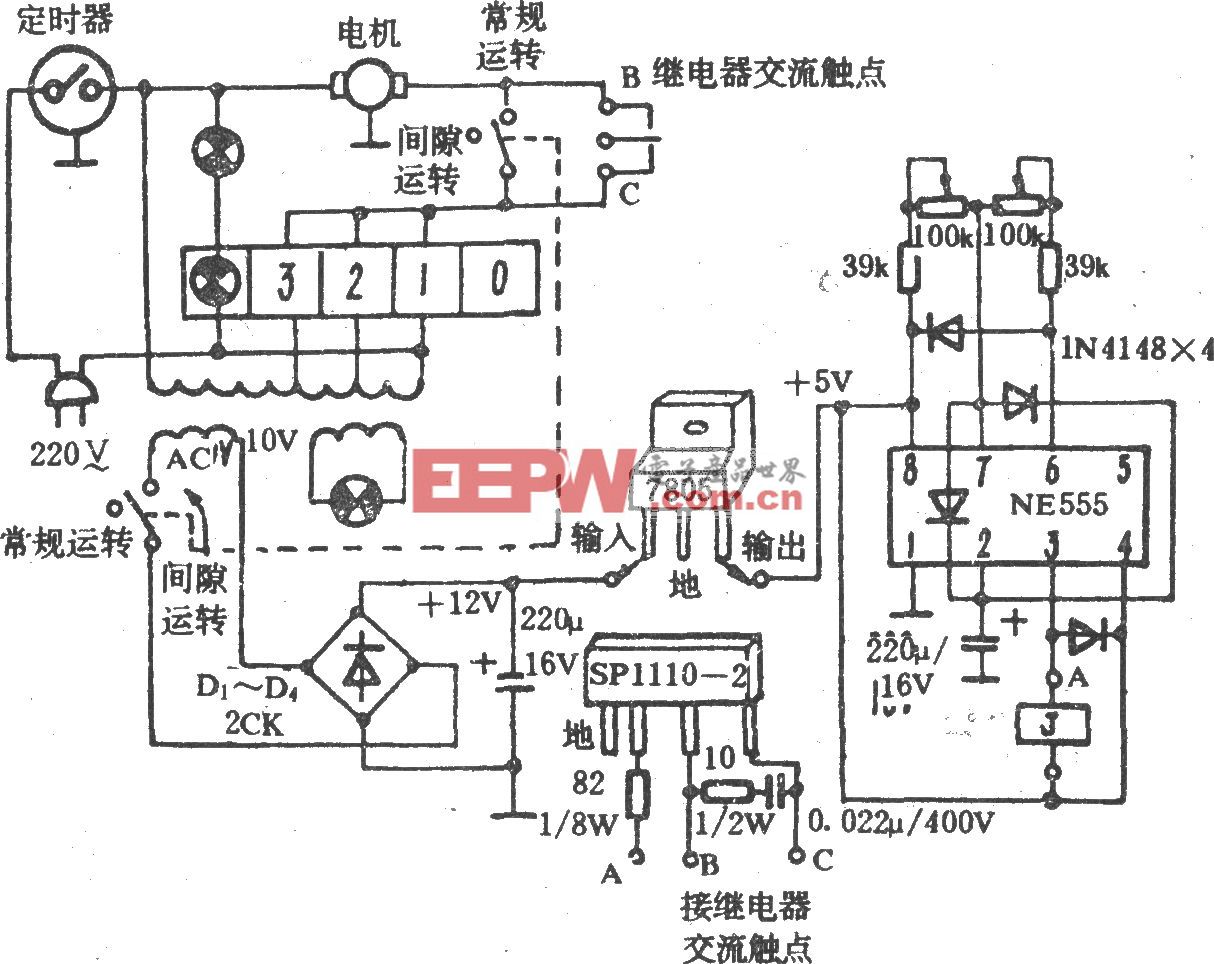

时钟数据恢复

如图8 所示, Altera 的高速CDR 电路使用混合体系结构,支持两种工作模式,进一步发展了传统的数据驱动体系结构。可以自动或者手动设置这两种模式――锁定至数据和锁定至参考。采用参考时钟作为输入,将CDR 单元中的模拟PLL 锁定到需要的频率上。然后,电路从参考时钟输入切换到数据信号, CDR 和数据信号实现相位锁定,从而恢复数据中的时钟。这种体系结构的关键优势在于缩短了锁定时间,降低了功耗,能够承受较大的抖动。结果, Altera 的收发器在驱动背板时,具有最低的抖动和最好的BER 性能,BER 达到10EC12 以上,而且协议兼容性非常好。

8

图8. CDR 体系结构

时钟产生和PLL 技术

时钟产生是高速收发器的一项重要功能。时钟抖动会影响发射器和接收器的性能,从而影响高速链路的BER 性能。PLL 的关键组成是振荡器,它是抖动的主要来源。理想情况下,高速压控振荡器(VCO) 提供较宽的调谐范围,较高的频率(GHz),较低的噪声和功耗,体积很小,集成度较高。

Altera 的高速收发器支持两类振荡器,环行振荡器(RO) 和LC谐振振荡器(LC谐振腔)。RO的集成度较高,功耗也比较低,管芯面积较小,在较宽的调谐范围内都具有优异的抖动性能,每一接收通道都有独立的RO,工作范围在600 Mbps 至10.3 Gbps。然而,随着频率的提高,相位噪声和抖动性能出现劣化,当高频时需要优异的相位噪声和抖动性能时, LC 谐振振荡器则显示出很大的优势。LC 谐振振荡器的缺点是其电感和可变电容( 变容),这些都是体积较大的元件。

■ 发送通道RO

● 在较宽的频率范围内具有优异的抖动性能

● 600 Mbps 至10.3 Gbps 的数据工作范围

■ 发送通道LC 谐振振荡器

● 技术实现了较好的抖动性能,较窄的工作范围。

● 4.9C6.375 Gbps LC 谐振振荡器,适用于PCIe/CEI-6。

● 9.9C11.3 Gbps LC 谐振振荡器 ,适用于XLAUI/CAUI/CEI-11G。

预加重和均衡

所有传输介质普遍存在的一个问题是由频率引起的损耗,特别是趋肤效应和电介质损耗导致的印刷电路板(PCB) 设计损耗。这种损耗导致高频分量的衰减更大,从而降低了远端信号的接收能力,缩短了驱动长度,增大了BER。预加重和均衡用在Altera 的高速收发器中,以克服传输损耗,驱动带有两个连接器的40

FR-4 背板。

在数据信号发送至通道之前,高速收发器的发射器采用预加重技术放大数据信号的高频分量。由于所生成数据信号的前面和后续数据位在发射器中是确定的,因此,预加重方法应用在相对于主脉冲的不同数据位上。Altera 的预加重方案使用预抽头,其后是主脉冲和两个后抽头。

在接收器开始进行均衡,当数据进入接收器时,均衡起到了高通滤波器的功能,成功地重建信号。Altera的高速收发器支持各种均衡方案(4):

Altera 公司 采用带有收发器的全系列40-nm FPGA 和ASIC 实现创新设计

9

■ 连续时间线性均衡(CTLE)

■ 自适应散射补偿引擎(ADCE)(5)

■ 判定反馈均衡(DFE)

由于不同的数据速率和背板特性,因此,很难从数千种设置中选择最佳均衡设置。使用收发器HSPICE 模型和背板S 参数特性进行仿真可以简化这一过程。但是,某些应用在工作中需要插拔系统卡,当条件变化时,不得不迅速更新均衡设置。利用即插即用信号完整性功能, Altera 引入了ADCE,热插拔收发器支持在40 FR-4 背板上2.5 Gbps 至6.5 Gbps 的数据传输。

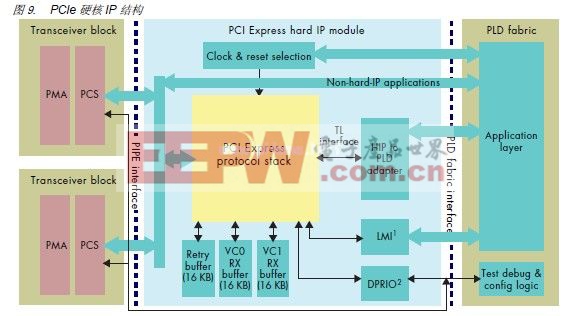

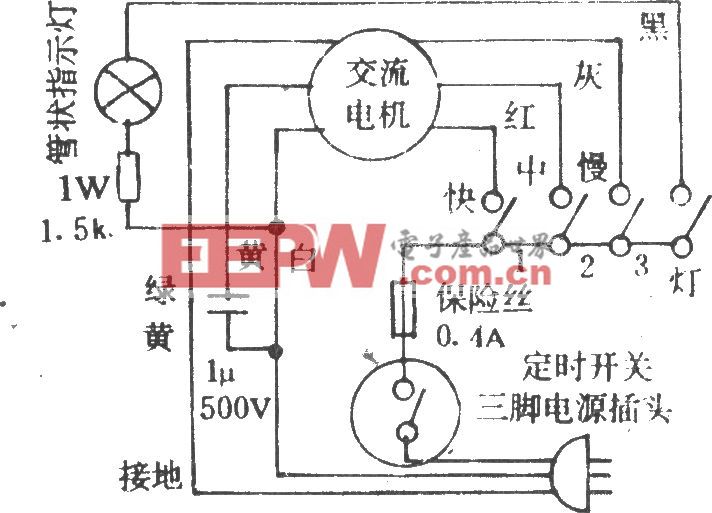

面向PCI Express 的硬核IP

PCIe 的广泛应用推动了集成PCIe 功能的发展,在实际中它作为预验证和符合标准的硬核IP 模块来实现。

PCIe 的重要优势是能够大大节省资源( 最大40K LE),降低功耗,其编译时间更短,从而缩短了设计周期。

如图9 所示,硬核IP 模块嵌入在PCIe 协议栈的所有层中,包括收发器模块、物理层、数据链路层和协议层。PCIe 硬核IP 模块符合以下PCI-SIG 规范:

■ PCIe 基本规范, Rev 1.1 (2.5 Gbps)

■ PCIe 基本规范, Rev 2.0 (2.5 和5.0 Gbps)

图9. PCIe 硬核IP 结构

注释:

(1) LMI:本地管理接口

(2) DPRIO:动态部分可重新配置输入/ 输出

Altera 的收发器系列器件

新器件的发展符合摩尔定律――密度每两年加倍,开发新器件需要不同的方法,由于开发成本随之增加,应尽量采用相关的技术。在开发全系列收发器FPGA 和ASIC 时, Altera 采用了以下方法:

■ 重新使用已有工艺所采用的技术

■ 通过技术进步,发挥每一新工艺节点的优势来逐步改进。

10

■ 使用通用体系结构,综合考虑不同的性能、功耗和成本要求,优化构建模块。

■ 进行革命性的创新,以满足重新使用已有技术所不能解决的需求。

系列产品组成

基于TSMC 的40-nm 工艺, Altera 采用了相同的成熟收发器体系结构来开发每一带有收发器的FPGA 和ASIC,这种结构非常适合宽带串行接口应用。在每个器件中,集成收发器模块针对目标应用进行了优化。

Arria II GX FPGA

Arria® II GX FPGA 满足了对成本和功耗敏感的应用,在低密度和中密度范围内提供丰富的特性。最大收发器数据速率是3.75 Gbps,满足了GPON、IP DSLAM、远程射频前端、广播和桥接等中等性能应用领域对高速协议和宽带的需求。收发器和I/O 经过优化,综合考虑特性和性能,具有较高的性价比。虽然Arria IIGX FPGA 的固定功耗模式不具有可编程功耗技术的灵活性,但是,它大大降低了静态功耗。Arria II GXFPGA 采用可编程预加重和均衡技术,适合背板应用,并且具有优异的信号完整性。由于只有速率较高的背板应用才需要ADCE 和DFE 等功能,为降低成本和功耗,该器件不支持这类功能。

Stratix IV GX FPGA

Stratix IV GX FPGA 提供最大的密度,最好的性能以及最低的功耗,收发器速率高达8.5 Gbps, 48 个收发器提高了带宽,其丰富的功能可支持背板应用和高速协议。关键应用包括对性能要求较高的无线基站、40G/100G 应用、高端路由器和桥接应用。其优异的信号完整性保证了与PCIe Gen2 和CEI-6 等严格协议的兼容性。可编程功耗技术提高了设计中关键时序通路的性能,同时优化了性能较低部分的功耗。

评论