在40-nm 工艺节点实现世界上最先进的定制逻辑器件

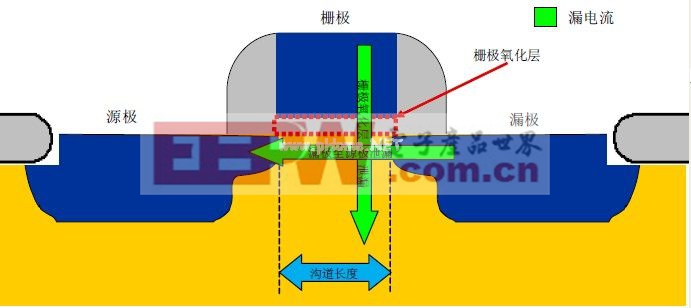

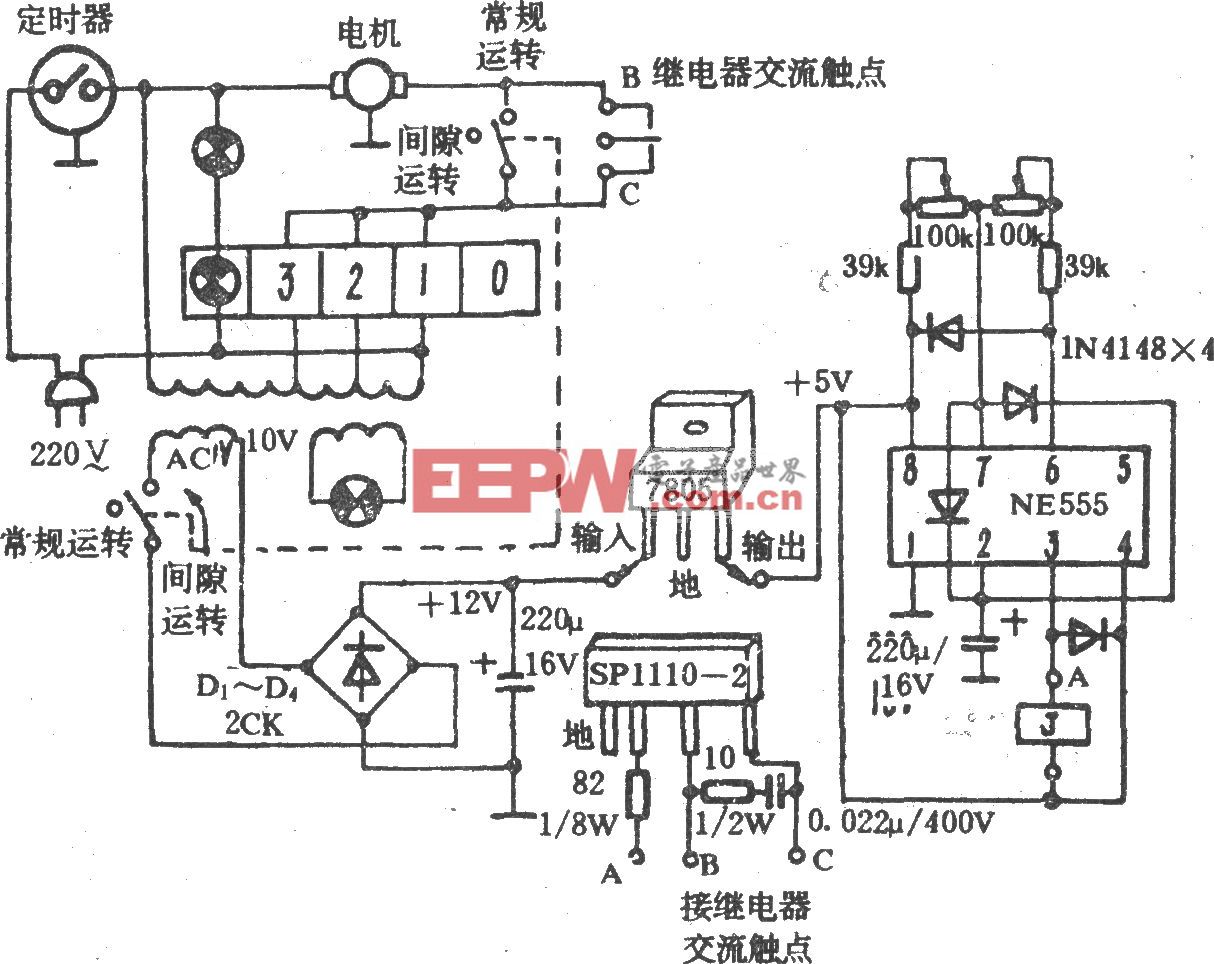

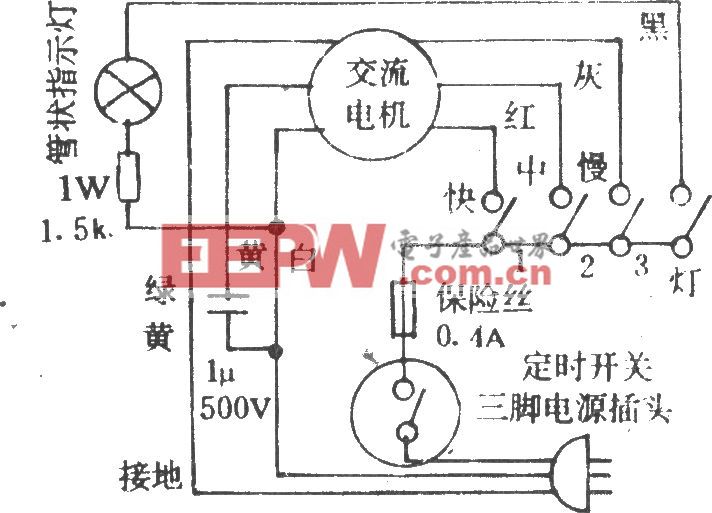

在深亚微米,随着向高级工艺的过渡,由于静态功耗显著增大,半导体功耗成为非常关键的问题。物理距离减小更容易出现电流泄漏。漏极至源极泄漏和栅极泄漏都与沟道长度和逻辑门氧化层厚度成反比,随着长度和厚度的减小会显著增大( 图2)。

NMOS

PMOS

Altera 公司 在40-nm 工艺节点实现世界上最先进的定制逻辑器件

3本文引用地址:http://www.eepw.com.cn/article/191799.htm

图2. 晶体管源极漏电流

源极至漏极泄漏也被称为亚阈值泄漏,是漏电流的主要因素。在这里,即使晶体管逻辑门关断,电流也会从晶体管源极流向漏极。由于晶体管越来越小,很难防止出现这类电流,因此,在其他参数都相同的条件下,较小的40-nm 晶体管比大工艺尺寸的晶体管更容易出现源极至漏极泄漏,而且漏电流更大。

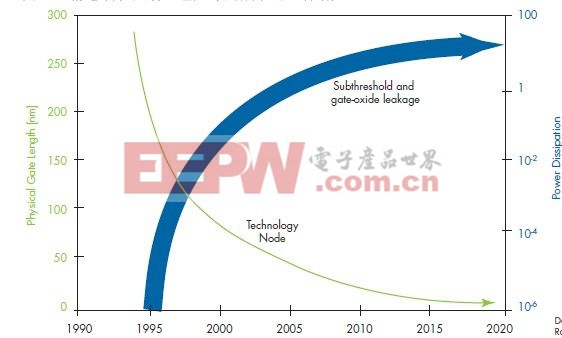

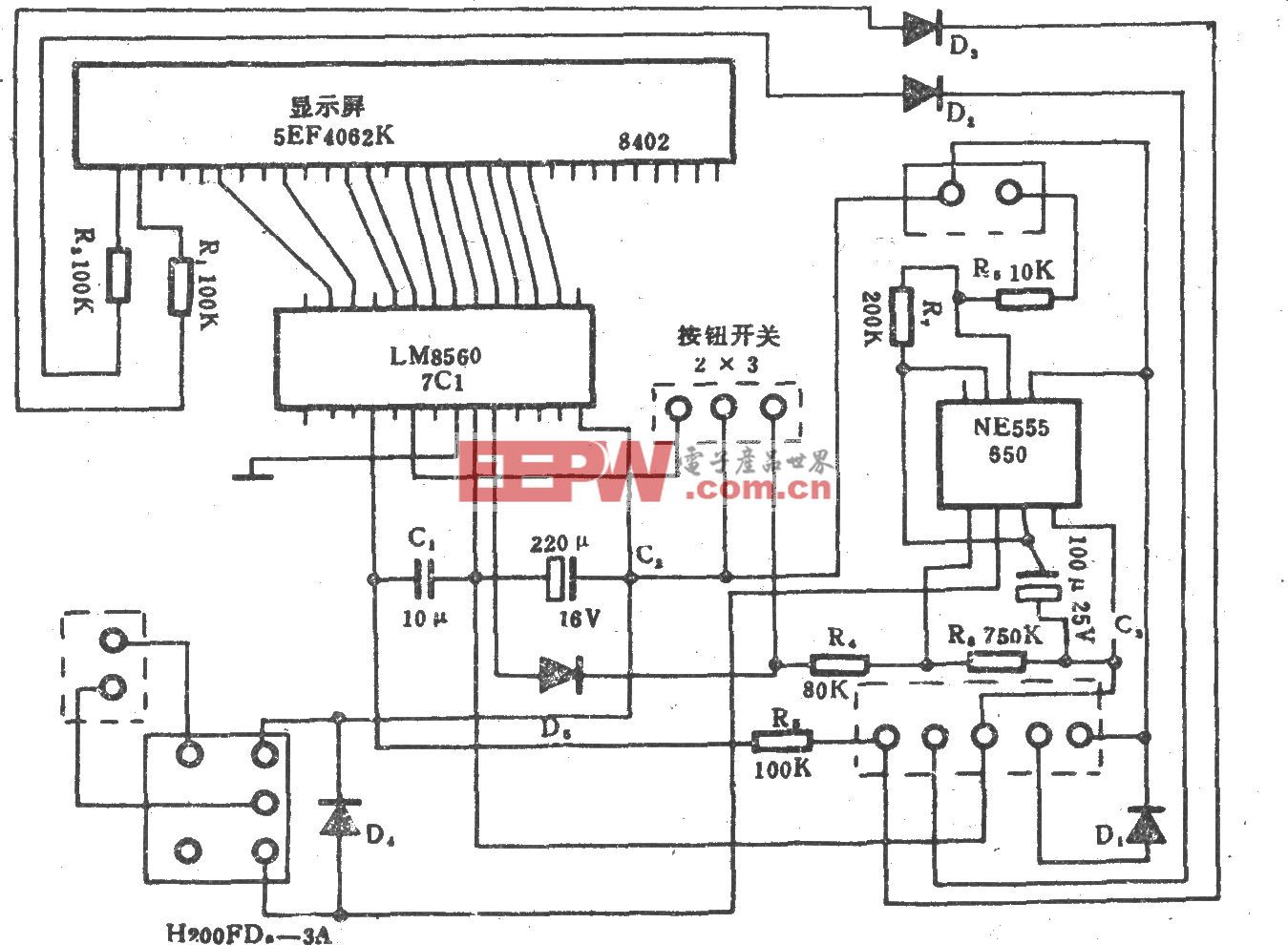

晶体管阈值电压(Vt) 也会影响源极至漏极泄漏的大小。晶体管Vt 是沟道开始传导栅极和源极之间电流的电压值。较小的高速晶体管需要较低的Vt 通过栅极控制来保持晶体管打开和关断的速率,但是由于晶体管沟道不能彻底关断,这也会增加漏电流。另一问题是栅极氧化层的厚度,它和搀杂一起也会影响Vt。较薄的氧化层使晶体管能够更迅速地开关,但是也增加了从栅极到基底氧化层的漏电流。随着工艺尺寸的减小,逻辑门长度越来越短,这些漏电流在增大,如图3 所示。

图3. 静态功耗随着工艺尺寸的减小而显著增大

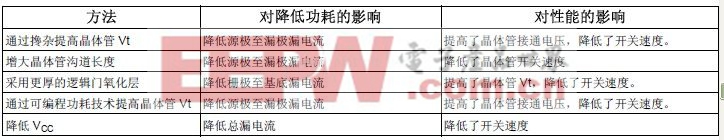

Altera 主要采用5 种方法来降低漏电流,如表3 所示。

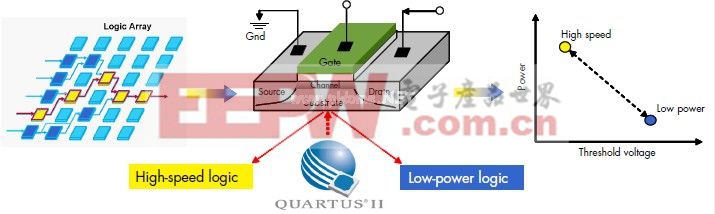

所有方法都对性能有影响,使晶体管不能以最大速率工作。然而, Altera 进行了明智的选择,在晶体管级以性能换取低功耗,维持器件总体性能不变。通过分析除了上面介绍的5 种方法, Altera 采用了其独特的可编程功耗技术来降低静态功耗。这一专利功能内置在Stratix IV 器件芯片中,使Quartus® II 开发软件能够根据设计要求,改变晶体管Vt,以平衡性能和功耗。图4所示为可编程功耗技术的高级实现, Quartus II 软件根据时序驱动的编辑功能分析用户FPGA 设计,选择逻辑阵列中的哪些晶体管应该采用高速模式,哪些应该采用低功耗模式。通过改变跨过反向偏置电压的晶体

管Vt,减小了时序不重要通路上的晶体管泄漏( 增大Vt),从而实现了低功耗,同时在需要的地方保持高性能不变。

图4. 可编程功耗技术 (1) 通过设置晶体管反向偏置,平衡了功耗/ 性能。

注释:

(1) 这是可编程功耗技术非常简单的“模型”。实际情况各种各样,并拥有专利。

为降低器件的动态功耗,在40-nm 器件上, Altera 将以前器件系列使用的1.1V 内核电压降到了0.9V。晶体

管开关期间消耗的功率与V2C ( 其中, C 是电容) 成正比,因此,降低供电电压会导致动态功耗按平方比

例下降。

减小内核电压也会影响晶体管性能,但是Altera 再次利用了40-nm 节点的高性能特性来保持器件级性能不变。如前所述,和以前的工艺节点相比, Altera 在40-nm 节点某些晶体管上具有更强的驱动能力, IC 设计人员能够在驱动能力和降低功耗上达到平衡。

此外, Altera 在其收发器上降低了每个发送器和接收器通道的功耗,进一步降低了总功耗。Altera Stratix

IV FPGA还通过动态片内匹配(OCT) 技术降低了有功功耗。采用动态OCT后,可以根据需要来接通或者关断Altera 器件中的匹配电阻。在存储器读/ 写周期中,关断不需要的匹配电阻,去掉了电阻上的压降,对于72 位接口,功耗能够降低1.2 瓦。

表3. Altera 降低漏电流采取的方法

方法对降低功耗的影响对性能的影响

通过搀杂提高晶体管Vt 降低源极至漏极漏电流提高了晶体管接通电压,降低了开关速度。

增大晶体管沟道长度降低源极至漏极漏电流降低了晶体管开关速度

采用更厚的逻辑门氧化层降低栅极至基底漏电流提高了晶体管Vt,降低了开关速度。

通过可编程功耗技术提高晶体管Vt 降低源极至漏极漏电流提高了晶体管接通电压,降低了开关速度。

降低VCC 降低总漏电流降低了开关速度

5

总之, Altera 在Arria II GX 器件上采取低功耗技术后,实现了带有3.75-Gbps 收发器、功耗最低的FPGA,其功耗比竞争器件低65%。对于Stratix IV FPGA,采取低功耗措施后,和65-nm Stratix III FPGA 中实现的相似设计相比,总功耗( 待机功耗 + 动态功耗) 平均降低了30%。

从技术领先到平稳提高产量成功推出首款40-nm FPGA 是非常重要的事件,但是Altera 的目标不止于此,还要象以前工艺节点产品那样,实现高质量可靠交付。通过努力, Altera 依靠其可靠的开发实践,包括强大的测试芯片计划、严格的器件检验程序以及在提高产量上的独特优势,获得了极大的成功。所有这些方面都得到了业界坚实的代工线合作伙伴的有力支持。

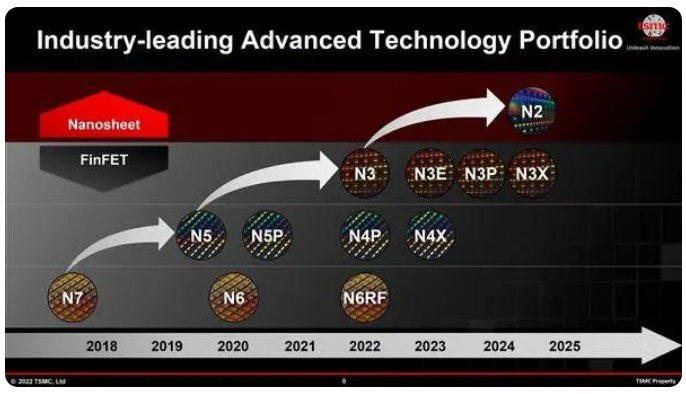

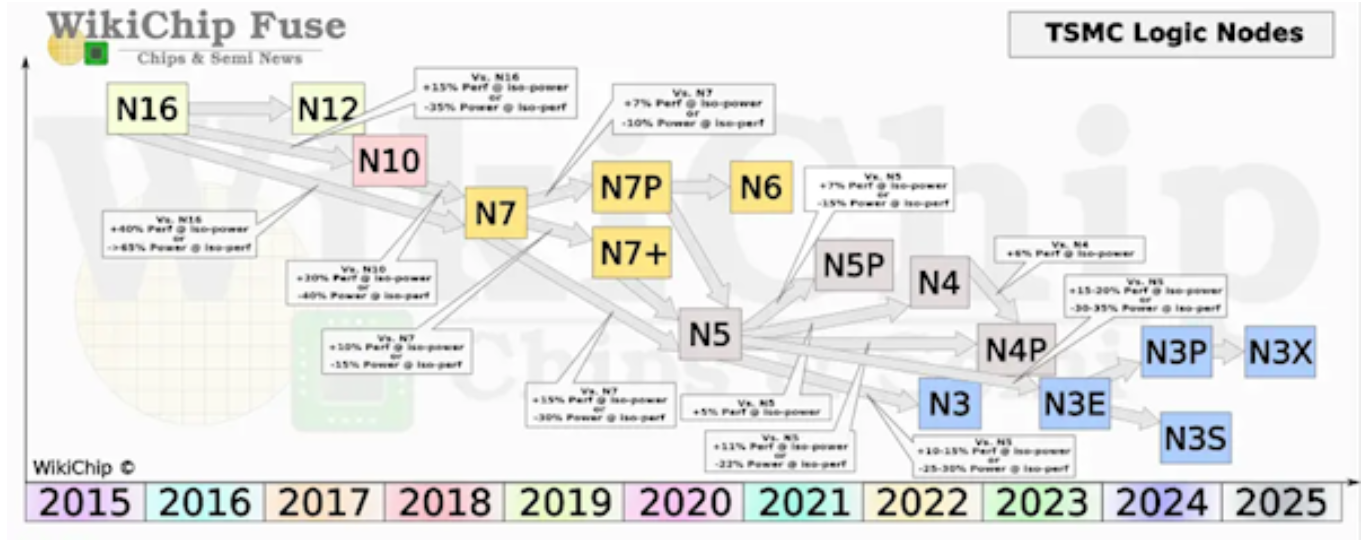

Altera 的代工线合作伙伴TSMC 是代工线市场的领先者。在专业代工线领域,TSMC 占据了50%以上的世界市场份额,年度研究和开发投入超出最相近竞争对手55%。这些投入使TSMC 在光刻和可生产性设计(DFM) 方面占据了业界领先位置,进一步保证了TSMC 能够成功交付高级工艺节点产品。最重要的是,在40-nm 节点, TSMC 是浸入式光刻技术的领先者,该工艺结合光刻透镜和清澈液体,透过分辨率更高的光线,实现了更小、封装更紧凑的器件。浸入式光刻是大部分半导体公司开发45-nm 节点及后续节点技术所选用的工艺,普遍认为也是32-nm 节点要采用的技术。

和TSMC 一起, Altera 积极组织了多个联合工艺开发团队,以解决工艺开发面临的各种问题,包括功耗/性能、建模、测试芯片规划、存储器、可靠性、聚乙烯熔丝、DFM、RF/ 模拟、ESD 和封装等。所有团队在双方产品交付和先进性上达成一致,精诚合作,坚持到底。

业界最可靠的测试芯片技术Altera 的实践表明,在130nm、90nm 和65-nm 器件生产中,对于新半导体工艺体系结构和器件特性的早期评估以及精细加工,测试芯片技术是非常有价值的工具。这一策略使Altera 的器件产量稳步上升,已经证明是可编程逻辑行业最具特色的一点。在40-nm 节点, Altera 以可靠的9 种测试芯片计划为其最新一代产品获得成功再次建立了强大的基础。

由于需要大量的模板,采用测试芯片意味着较大的投入。Altera 与TSMC 密切合作,保持了工艺效率,降低了成本。例如, TSMC 自己制造大量的测试晶片,全面进行特性测试,调整制作方法,然后监控产品。

通过密切合作,在代工线晶片早期阶段实现了“背负式”测试结构,缩短了Altera 产品投产时间,使客户能够尽早使用最先进的技术。同样的,在Altera 的帮助下, TSMC 能够有机会使用其模板进行更多的测试。结果对双方都有好处。

通过采集并分析测试芯片数据, Altera 深入研究了各种随机和系统偏差的影响,开发设计策略来降低甚至消除这些不利影响。Altera 在测试芯片上的大量投入帮助客户避免了前沿半导体设计中的风险。对风险管理的关注展示了Altera 在可靠交付新技术产品上的承诺, Altera 不会中断或者以有限的产量向客户供货,也不会提供达不到要求的产品。

评论