基于IDT75K62100 芯片的硬件控制库设计

1 前言

本文引用地址:https://www.eepw.com.cn/article/158039.htm针对Internet 的安全需要,为了给IPV4 和IPV6 数据报提供高质量的、可互操作的、基于密码学的安全性,Internet 工程任务组(IETF)颁布了IP 层安全标准IPSec。IPSec 在IP 层对数据包进行高强度的安全处理,提供包括访问控制、无连接的完整性、数据源认证、抗重播(replay)保护(序列完整性(sequence integrity)的一个组成部分)、保密性和有限传输流保密性在内的服务。这些服务是基于IP 层的,提供对IP 及其上层协议的保护。

对于IPSec 数据流处理而言,有两个必要的数据库:安全策略数据库(SPD) 和安全关联数据库(SAD)。SPD 指定了用于到达或者源自特定主机或网络的数据流的策略,而SAD 则包含了活动的SA 参数。在启动IPSec 保护的源和目的之间,都需要设置单独的输入和输出SPD 和SAD 。

经受IPSec 保护的节点的通信流,无论是输入还是输出都必须查询SPD。SPD 包含一个策略条目的有序列表,每个条目里又包含多个选择符,输入输出数据流就是通过和这些选择符比较来决定是否进行安全保护。IPSec 允许的选择符有目的IP 地址,源IP 地址,传输层协议,系统名和用户ID。目的和源IP 地址可以是一个主机地址,广播地址,单播地址,任意播地址,地址范围,地址加子网掩码或者通配地址;系统名和用户ID 可以是完整的DNS 名或E-mail 地址。SPD 中的条目决定了处理通信流的粒度,策略可能规定与某特定的SA 或SA 束对应的IPSec 服务应该应用到任何源自任何源或者去往任何目的地的所有通信流,策略也可能规定应该基于特定的选择符来决定不同SA 或SA 束的应用。总之,SPD 在控制通过一个IPSec 系统的所有通信中发挥着非常重要的作用。为了在保证安全强度的前提下,提高IPSec 保护节点上的流处理速度,本文提出了一种采用硬件IDT75K62100 芯片实现快速的SPD 与SAD 数据库的思想。

2 SPD 与SAD 硬件结构

安全模块的设计初衷就是为了在IPV6 路由器中对特定的数据流实现高速的IPSec 安全保护,这就使得SPD 和SAD 的高速查找成为一个很关键的问题,因为对每一个包进行IPSec 处理时,都必须查找SPD 和SAD 以获取相应的处理策略,如果查找速度慢的话,将达不到高速的性能要求。数据库可以用软件来组织,也可以依托硬件来实现,为了提高查找速度,我们使用硬件来做数据库。目前支持高速查找的硬件主要有两种:基于逻辑算法设计的SRAM 技术和基于半导体器件设计的CAM(Content Addressable Memory, 内容寻址寄存器)技术。常用的随机存储器通过输入地址来返回该地址所对应的数据信息,而CAM 只需要输入关键字的内容就会将此关键字与CAM 中所有表项同时进行比较,最后返回匹配表项在CAM 中对应的地址信息。CAM 可以在一个硬件时钟周期内完成关键字的精确匹配查找,目前速度可达到266Mpps 。

CAM 虽然有很多优势,但在本模块中如果都采用CAM 来作为数据库,则一方面代价太高,因为输入处理和输出处理各需要两个数据库(SPD和SAD), 这样一共需要四个CAM,而CAM 价格较为昂贵;另一方面将SPD 和SAD 分别设在两块CAM 中,这样每处理一包需要进行两次查找,影响了速度。为此,我们特别研究了一种能够实现快速查找的数据库硬件结构,这种结构采用CAM 和SRAM 相结合的方式。这种结构一方面在一定程度上降低了成本,另一方面解决了二次查找的问题。

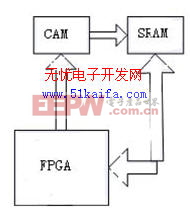

这种硬件结构的组成原理是将SPD 设置在CAM 中,而将SAD 设置在SRAM 中,然后将CAM 和SRAM 级联。这样,在进行IPSec 处理时,先在CAM 中查SP,如果没有找到相应的SP, 则查找结束;如果查到了相应的SP,则由CAM 将对应的SA 在SRAM 中的存放地址送给SRAM, 然后从SRAM 中对应地址将SA 取出送FPGA, 这样避免了再由FPGA 对SAD 进行查询。这种数据库的查找方法还引入了流水机制,即CAM 查到了前一报文的SP 后,将匹配地址送给SRAM,在SRAM 读该地址对应的SA 的同时,CAM 可进行对下一报文的SP 的查找。该查找方法中,CAM 与SRAM 的连接如图一所示。

图 1 :CAM 与SRAM 连接图

3 75K62100 芯片的内部结构 实际设计中,CAM 选用IDT 公司的75K62100 ,其内部逻辑结构与主要外部总线如图二所示。从图中可以看出,该型号CAM 内部主要由配置电路,指令译码,输入输出数据缓存,比较寄存器和数据存储区等单元组成,外部总线有指令总线,数据总线和索引总线,另外还包括一条匹配标志信号线。该CAM 的数据存储区的容量为18M, 经过配置电路配置,可以工作在256k×72bit (表项深度为256K, 宽度为72bit)、128K×144bit 、72K×288bit 等模式下。指令总线宽20 位,配置指令,读写指令从该总线输入。数据总线宽72 位, 输入数据时,先将数据写入数据输入输出缓存区,在内部地址译码控制下,再将数据写入数据存储区或比较寄存器。比较后得到匹配项的地址由24 位索引总线送出,数据经输入输出缓存器从数据总线输出,并由匹配标志信号线给出匹配状态。

评论