基于IDT75K62100 芯片的硬件控制库设计

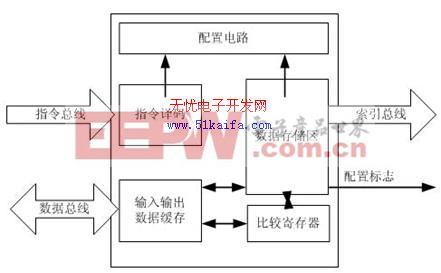

图 2 :IDT75K62100 内部逻辑结构与外部总线示意图

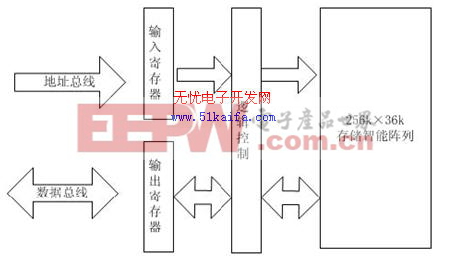

SRAM 选用IDT 公司的71V65603 ,该款SRAM 工作频率为100M-150MHZ ,支持ZBT 技术,容量为256KX36bit 。其内部逻辑结构及主要外部总线如图三所示。

图 3 :IDT71V65603 内部逻辑结构与外部总线示意图

查找时,先从包头中提取出查表关键字送CAM 查SP,若查到了SP,则将此SP 对应的SA 的地址通过CAM 索引总线送给SRAM 并将匹配标志送IPSec 处理单元,SRAM 根据送来的地址将对应的SA 通过数据总线写入IPSec 处理单元。每查到一条SA,则需要对SAD 中的该SA 条目进行更新,因为SA 中包括序列号和SA 生存期等需要及时更新的字段。更新过程和查找过程基本一致,先从CAM 中找到对应的SP 条目,得到该SA 的存放地址,然后将修改后的SA 写入该地址或将原SA 删除。

一个好的IPSec 协议实现方案,一定程度上取决于SPD 和SAD 条目的合理的设置,因为合理的SPD 和SAD 条目设置可以使IPSec 处理即不复杂,又达到了预期的安全保护的要求。

根据实际需要,本安全模块的SPD 中每个条目设置源IP 地址,目的IP 地址,传输层协议三个选项。需要注意的是,源IP 地址和目的IP 地址项完全没必要设为128 位的, 只需要储存各自地址的高64 位即可,因为在128 位的IPV6 地址中,高64 位是所属网络地址,由于是在路由器上实现IPSec 保护,故在进行策略查找时,只需要检查数据包中的源和目的的网络地址是否与策略库中的网络地址相匹配即可。传输层协议选项为8 位宽,对于输出处理单元,只对TCP 和UDP 进行安全保护,故该选项的十进制值应为6(TCP)或17(UDP)

; 对于输入处理单元,只对ESP 进行处理,故该选项的十进制值应为50。由此看来,SPD 的表项宽度应在136 位以上。

对于输出包处理的SAD,每个SA 条目包括SPI 字段,序列号计数器字段,序列号溢出字段,密钥字段和SA 生存期字段。其中,SPI 字段为32 位宽, 取值范围为256―232-1,我们规定,若SPI 为全1,则表示SA 尚未建立,需要进行协商;若SPI 为其它有效值,则根据对应的SA 进行安全处理。序列号计数器字段为32 位宽,为所处理的数据包提供一个唯一的编号用来抗重放。序列号溢出字段为1 位宽,当该位为‘1’时,表示需要对序列号字段进行溢出检查;为‘0’表示不需进行溢出检查。密钥字段128 位,存放3DES 算法的密钥。SA 生存期字段16 位宽, 值为预先约定的该SA 所处理的数据包的个数,每处理一包该值减一,为0 时该SA 过期, 重新协商。综上所述,输出包处理的SAD1 每个表项宽度应在209 位。

评论