楷登电子(美国 Cadence 公司)今日发布业界首款已通过产品流片的第三代并行仿真平台Xcelium™ 。基于多核并行运算技术,Xcelium™ 可以显著缩短片上系统(SoC)面市时间。较Cadence上一代仿真平台,Xcelium™ 单核版本性能平均可提高2倍,多核版本性能平均可提高5倍以上。Cadence® Xcelium仿真平台已经在移动、图像、服务器、消费电子、物联网(IoT)和汽车等多个领域的早期用户中得到了成功应用,并通过产品流

关键字:

Cadence Xcelium

楷登电子(美国 Cadence 公司)与西安电子科技大学共同宣布,Cadence将与西安电子科技大学携手共建集成电路设计培训中心(下称“联合培训中心”),并在西安电子科技大学隆重举行了西电、CSIP、Cadence战略合作会议暨联合培训中心揭牌仪式。西安电子科技大学副校长李建东和Cadence全球副总裁兼亚太区总裁石丰瑜先生,与陕西省工业和信息化厅电子信息处处长高翔和工业和信息化部软件与集成电路促进中心集成电路处负责人霍雨涛共同为联合培训中心进行揭牌。在揭牌仪式之后,西安电子科

关键字:

Cadence 集成电路

益华电脑(Cadence Design Systems, Inc.)宣布,展讯通讯(上海)公司(Spreadtrum Communications (Shanghai) Co., Ltd.,)运用全新的 Cadence Innovus 设计实现系统,大幅缩短数百

关键字:

展讯 Cadence

ARM®今日宣布加强在中国的战略部署,与重庆市政府、重庆仙桃数据谷达成多项协议,建立合作计划,共同推进重庆仙桃数据谷电子产业创新生态圈建设。当日,双方共同为位于仙桃数据谷的ARM生态产业园揭幕;并宣布成立重庆地区ARM生态集成电路人才培养与产学研协同创新联盟,建立重庆ARM生态产业技术人才实训中心;此外,由ARM和中科创达共同投资的创业加速器安创空间宣布其重庆公司开业,正式落户重庆仙桃数据谷ARM生态产业园。

A

关键字:

ARM Cadence

Cadence设计系统公司今日宣布,正式交付完整的数字与签核参考流程,用于Imagination Technologies (IMG.L)公司PowerVR Series7图形处理单元(GPU)。采用此高度集成的Cadence® 参考流程,550万实例的完整合成与设计实现可在2.5天完成。对比上一代Cadence设计流程,产品开发设计时间缩短1倍以上。同时,采纳新参考流程后,芯片面积平均缩小3%,Imagination最复杂的组块面积可缩小达7%。

此参考流程操作简单,仅需单次执行;同时

关键字:

Cadence GPU

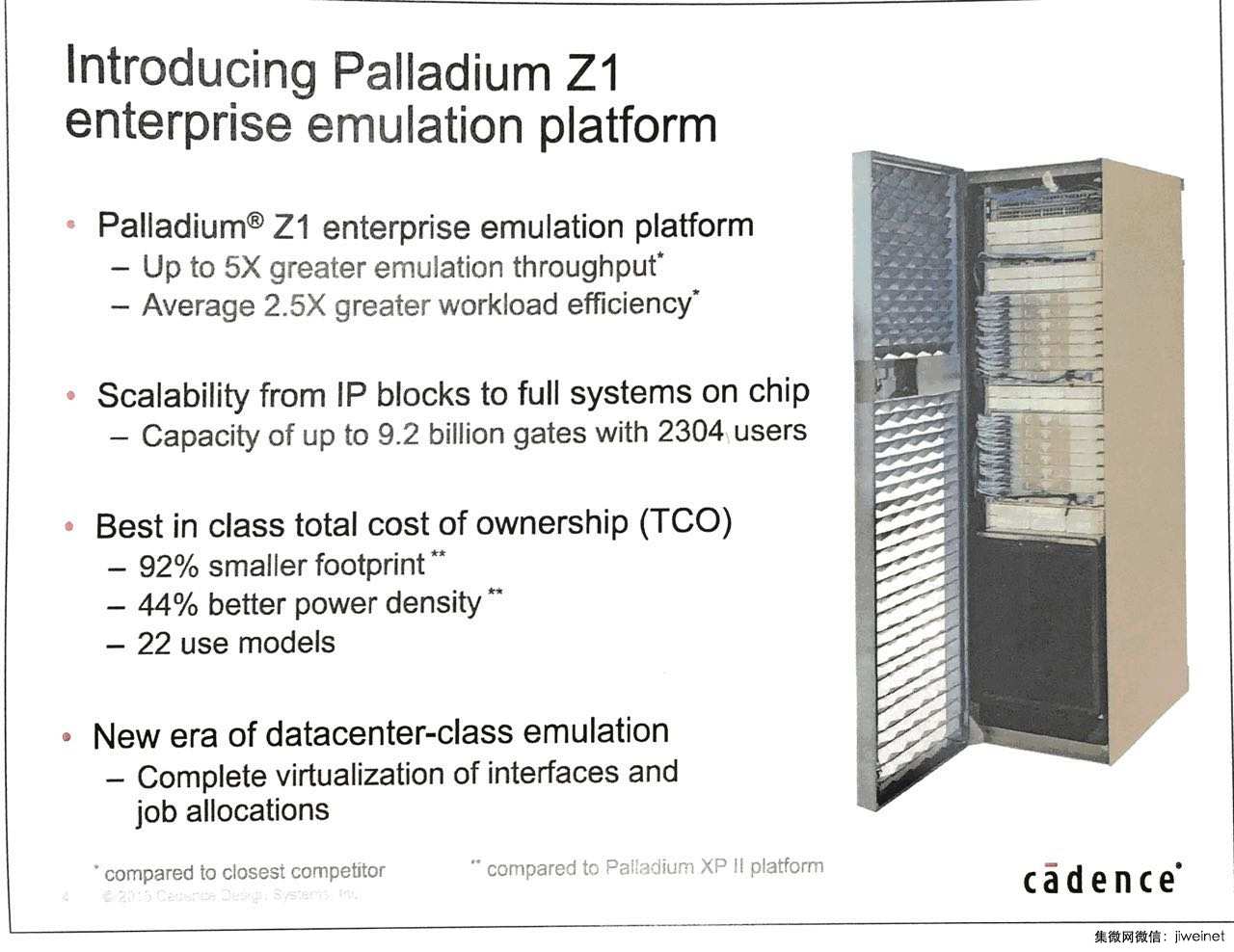

Cadence作为全球EDA电子设计自动化领导厂商,其Palladium平台自2001年推出以来,给众多系统芯片开发商在提高设计水平、验证以前无法实现的性能与扩展性方面带来了巨大的帮助。今天,Cadence正式推出Cadence Palladium Z1企业级硬件仿真加速平台。 Palladium Z1:业内第一个数据中心级硬件仿真加速器 据介绍,这是业内第一个数据中心级硬件仿真加速器,仿真处理能力是上一代产品(Palladium XP II)的5

关键字:

Cadence Palladium

两岸的IC设计公司在先进制程节点晶片设计和其复杂度的进展令全球半导体界瞩目。于此同时,对领先EDA工具的需求也持续上升。

Cadence在今年上半年推出了Innovus设计实现系统,称其为新一代的实体设计实现解决方案,使系统开发人员能够在先进的16/14/10奈米FinFET制程以及其他成熟的制程节点上交付最佳功耗、性能和面积(PPA)指标的设计。

2015年10月中旬,我拜访了Cadence位于美国矽谷的总部,与Cadence公司设计实作产品事业部的产品管理总监Vinay Patward

关键字:

Cadence IC设计

全球电子设计创新领先公司Cadence设计系统公司 (Cadence Design Systems, Inc.)宣布:将于8月13日(星期四)在上海浦东嘉里大酒店举办一年一度的中国用户大会——CDNLive China 2015!以“联结,分享,启发!”为主题的CDNLive大会将集聚超过700位IC行业从业者,包括IC设计工程师、系统开发者与业界专家,将分享重要半导体设计领域的解决方案和成功经验,让参与者获得知识、灵感与动力,并为实现高阶半导体芯片、S

关键字:

Cadence SoC

益华电脑(Cadence)推出下一代Cadence JasperGold形式验证平台,此新型形式验证解决方案将Cadence Incisive形式与JasperGold技术整合为单一平台,与以往解决方案相比,效能可增加至15倍。此外,整合至Cadence系统开发套装(Cadence System Development Suite)后,JasperGold技术可缩短验证时程达3个月。

JasperGold形式(formal)与形式辅助技术整合至Cadence系统开发套

关键字:

Cadence JasperGold

Cadence(Cadence Design Systems, Inc. )今天发布Cadence® Innovus™ 设计实现系统,这是新一代的物理设计实现解决方案,使系统芯片(system-on-chip,SoC)开发人员能够在加速上市时间的同时交付最佳功耗、性能和面积(PPA)指标的的设计。Innovus设计实现系统由具备突破性优化技术所构成的大规模的并行架构所驱动,在先进的16/14/10纳米FinFET工艺制程和其他成熟的制程节点上通常能提升10%到20%的功耗、性能和面

关键字:

Cadence SoC

Cadence今天宣布灿芯半导体(Brite Semiconductor Corporation)运用Cadence® 数字设计实现和signoff工具,完成了4个28nm系统级芯片(SoC)的设计,相比于先前的设计工具,使其产品上市时间缩短了3周。通过使用Cadence设计工具,灿芯半导体的设计项目实现了提升20%的性能和节省10%的功耗。

灿芯半导体使用Cadence Encounter® 数字设计实现系统用于物理实现、Cadence Voltus™ IC电源完整

关键字:

Cadence SoC

益华电脑(Cadence Design Systems)宣布,已与通讯网路与数位媒体晶片组供应商海思半导体(HiSilicon Technologies)已经签署合作协议,将于16奈米 FinFET 设计领域大幅扩增采用Cadence 数位与客制/类比流程,并于10奈米和7奈米制程的设计流程上密切合作。

海思半导体也广泛使用Cadence数位和客制/类比验证解决方案,并且已经取得Cadence DDR IP与Cadence 3D-IC 解决方案授权,将于矽中介层基底(silicon interp

关键字:

Cadence 海思 FinFET

曾经看到电脑主板的PCB的时候,心里想能自己画出来是多么棒的一件事情。后来接触到protel99se就步入了画板子的队伍,之后altium 、cadence等等。随着画板子的经历积累,发现需要注意的事项越来越多。一块好的PCB板子不是将连线连通就行,置于其中的故事,容我慢慢道来。

第一、大多数PCB的设计师都是是精通电子元器件的工作原理,知道其相互影响,更明白构成电路板输入和输出的各种数据传输标准。一个优秀的电子产品不但需要有优秀的原理图,更需要PCB布局和走线的人,而后者对最终电路板的成败起到

关键字:

PCB altium cadence

全球知名的电子设计创新领导者Cadence设计系统公司今日宣布其丰富的IP组合与数字和定制/模拟设计工具可支持台积电全新的超低功耗(ULP)技术平台。该ULP平台涵盖了提供多种省电方式的多个工艺节点,以利于最新的移动和消费电子产品的低功耗需求。

为加速台积电超低功耗平台的技术发展,Cadence将包括存储器、接口及模拟功能的设计IP迁移到此平台。使用Cadence TensilicaÒ数据平面处理器,客户可以从超低功耗平台受益于各种低功耗DSP应用,包括影像、永远在线的语音、面部识

关键字:

Cadence 台积电 FinFET

全球知名的电子设计创新领导者Cadence设计系统公司今日宣布为台积电16纳米FinFET+ 制程推出一系列IP组合。 Cadence所提供的丰富IP组合能使系统和芯片公司在16纳米FF+的先进制程上相比于16纳米FF工艺,获得同等功耗下15%的速度提升、或者同等速度下30%的功耗节约。

目前在开发16 FF+工艺的过程中,Cadence的IP产品组合包括了在开发先进制程系统单芯片中所需的多种高速协议,其中包括关键的内存、存储和高速互联标准。IP将在2014年第四季度初通过测试芯片测试。有关IP

关键字:

Cadence 台积电 FinFET

cadence介绍

EDA仿真软件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。其解决方案旨在提升和监控半导 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473