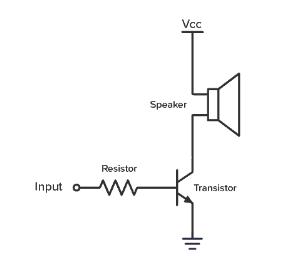

MCU-Creator 是基于 NXP LPC5528 做的 3D 打印机主板方案,该方案主控 MCU LPC5528 是一颗 Cortex-M33 内核的高性能 MCU,主频达到 150MHz,拥有 512KB 片上 Flash ,256KB RAM ,有多个 Timer,多路 PWM,多种通信接口,支持 16 位的 ADC,资源丰富。 该方案支持 3.5 寸触摸屏显示,480*320 分辨率,支持 SD 卡、 U 盘传输打印资料给打印机,支持 5 轴电机控制,支

关键字:

3D 打印机 NXP LPC5528

中国上海,2023 年 7 月 4 日 — Teledyne 将于 7 月 11-13 日在上海国家会展中心举办的 2023中国(上海)机器视觉展 (Vision China) 展示最新产品和解决方案。欢迎各位莅临 5.1A101 展位了解先进的 3D 解决方案,Teledyne DALSA、e2v 和 FL

关键字:

Teledyne Vision China 3D AI成像

1947年,当John Bardeen、Walter Brattain和William Shockley成功制造出了世界上第一个能正常工作的晶体管时,他们未曾想到,晶体管如今会成为电子产品的最重要组成部分。晶体管被誉为20世纪最伟大的发明之一,它改进了真空管在功耗和尺寸方面的缺陷,为电子设备的发展奠定了基础,也为人们带来了便捷高效的数字化生活。1947年,当John Bardeen、Walter Brattain和William Shockley成功制造出了世界上第一个能正常工作的晶体管时,他们未曾想到,

关键字:

新思科技 晶体管

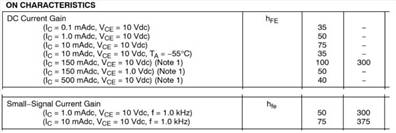

如果您施加一个足够高的电压 V IN以正向偏置基极-发射极结,电流将从输入端流过 R B,通过 BE 结,到达地。我们称之为 I B。电流还将从 5 V 电源流经 R C,流经晶体管的集电极到发射极部分,流到地。称之为I C。假设 I C足够小以在集电极端留下相对较高的电压——足够高的电压,即保持基极-集电极结反向偏置。假设我们正在使用一个简单的电路,该电路由一个 npn双极结型晶体管(BJT) 和几个电阻器组成,连接方式如下:如果您施

关键字:

晶体管

2023 年 5 月 24 日,中国—— 意法半导体的STL120N10F8 N沟道100V功率MOSFET拥有极低的栅极-漏极电荷(QGD)和导通电阻RDS(on),优值系数 (FoM) 比上一代同类产品提高40%。 新推出的MOSFET利用ST的STPOWER STripFET F8先进技术,引入氧化物填充沟槽工艺,集极低的导通损耗和低栅极电荷于一身,实现高效的开关性能。因此,STL120N10F8的最大导通电阻 RDS(on)为 4.6mΩ(在 VGS = 10V 时),高效运行频率达到6

关键字:

意法半导体 STripFET F8 晶体管 优值系数

MOS 晶体管正在按比例缩小,以限度地提高集成电路内的封装密度。这导致氧化物厚度的减少,进而降低了 MOS 器件的阈值电压。在较低的阈值电压下,漏电流变得很大并有助于功耗。这就是为什么了解 MOS 晶体管中各种类型的漏电流至关重要。MOS 晶体管正在按比例缩小,以限度地提高集成电路内的封装密度。这导致氧化物厚度的减少,进而降低了 MOS 器件的阈值电压。在较低的阈值电压下,漏电流变得很大并有助于功耗。这就是为什么了解 MOS 晶体管中各种类型的漏电流至关重要。在我们尝试了解各种漏电流成

关键字:

MOS 晶体管

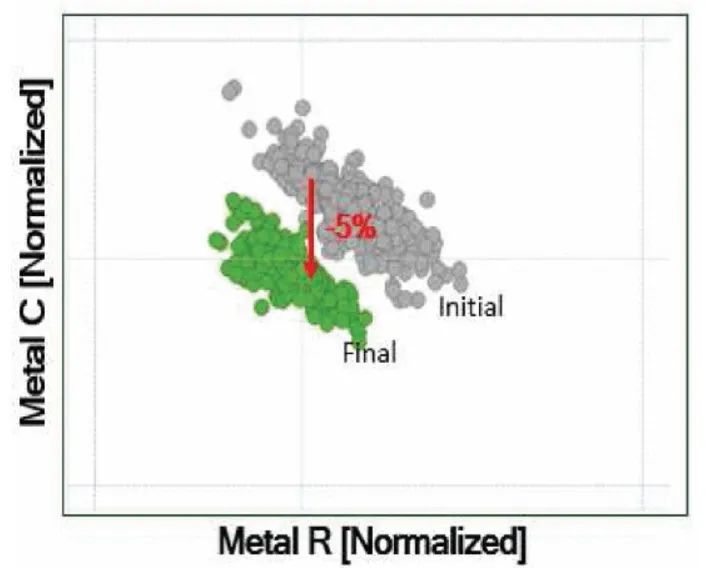

5 月 5 日消息, 铠侠和西数展示最新的技术储备,双方正在努力实现 8 平面 3D NAND 设备以及具有超过 300 条字线的 3D NAND IC。根据其公布的技术论文,铠侠展示了一种八平面 1Tb 3D TLC NAND 器件,有超过 210 个有源层和 3.2 GT/s 接口,可提供 205 MB/s 的程序吞吐量,读取延迟缩小到 40 微秒。此外,铠侠和西部数据还合作开发具有超过 300 个有源字层的 3D NAND 器件,这是一个具有实验性的 3D NAND IC,通过金属诱导侧向

关键字:

3D NAND

晶体管是一个简单的组件,可以使用它来构建许多有趣的电路。在本文中,将带你了解晶体管是如何工作的,以便你可以在后面的电路设计中使用它们。一旦你了解了晶体管的基本知识,这其实是相当容易的。

关键字:

晶体管

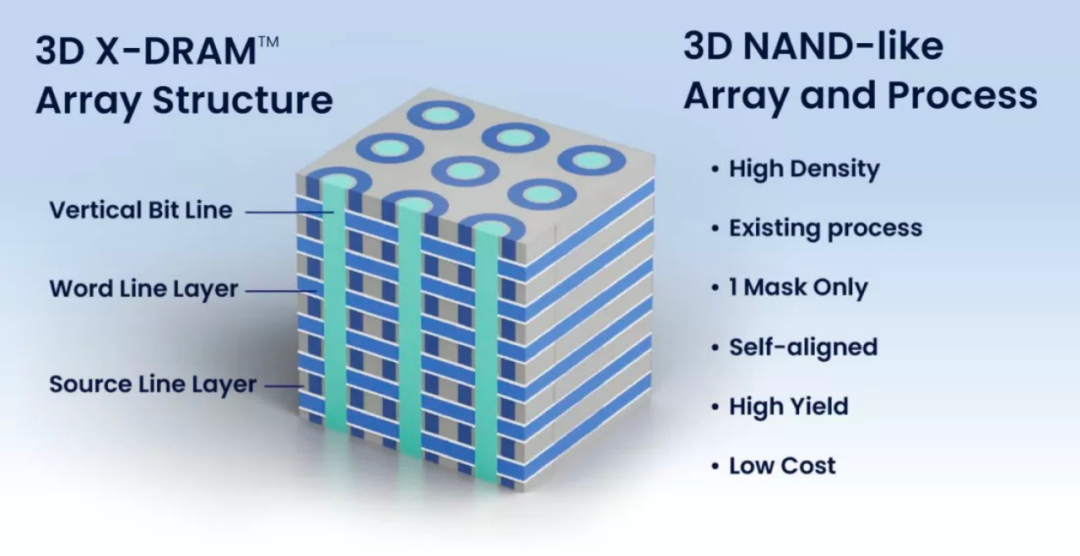

近日,外媒《BusinessKorea》报道称,三星的主要半导体负责人最近在半导体会议上表示正在加速3D DRAM商业化,并认为3D DRAM是克服DRAM物理局限性的一种方法,据称这将改变存储器行业的游戏规则。3D DRAM是什么?它将如何颠覆DRAM原有结构?壹摩尔定律放缓,DRAM工艺将重构1966年的秋天,跨国公司IBM研究中心的Robert H. Dennard发明了动态随机存取存储器(DRAM),而在不久的将来,这份伟大的成就为半导体行业缔造了一个影响巨大且市场规模超千亿美元的产业帝国。DRA

关键字:

3D DRAM 存储器

据外媒《BusinessKorea》报道,三星电子的主要半导体负责人最近在半导体会议上表示正在加速3D DRAM商业化,并认为3D DRAM是克服DRAM物理局限性的一种方法。三星电子半导体研究所副社长兼工艺开发室负责人Lee Jong-myung于3月10日在韩国首尔江南区三成洞韩国贸易中心举行的“IEEE EDTM 2023”上表示,3D DRAM被认为是半导体产业的未来增长动力。考虑到目前DRAM线宽微缩至1nm将面临的情况,业界认为3~4年后新型DRAM商品化将成为一种必然,而不是一种方向。与现有

关键字:

存储 3D DRAM

国内EDA行业领导者芯和半导体,由于其Metis平台在2.5D/3DIC Chiplet先进封装设计分析方面的杰出表现,近日在半导体行业国际在线平台3D InCites的评选中,获封2023“Herb Reiter 年度最佳设计工具供应商奖”称号。 “Xpeedic芯和半导体去年宣布Chipletz采用了Metis平台用于智能基板产品的设计,这一事件引起了我们极大的关注。“3D InCites创始人Françoise von Trapp表示,” 我们非常兴奋芯和半导体今年首次参加3D InCi

关键字:

芯和半导体荣 3D InCites Herb Reiter 年度最佳设计工具供应商奖

国内EDA行业领导者芯和半导体,由于其Metis平台在2.5D/3DIC Chiplet先进封装设计分析方面的杰出表现,近日在半导体行业国际在线平台3D InCites的评选中,获封2023“Herb Reiter 年度最佳设计工具供应商奖”称号。 “Xpeedic芯和半导体去年宣布Chipletz采用了Metis平台用于智能基板产品的设计,这一事件引起了我们极大的关注。“3D InCites创始人Françoise von Trapp表示,” 我们非常兴奋芯和半导体今年首次参加3D

关键字:

芯和半导体 3D InCites Herb Reiter年度最佳设计工具供应商奖

本系列连载将介绍电力电子相关的基础知识和各种小知识。本系列涉及到的内容很广泛,涵盖从基础知识到应用部分的丰富内容,希望能够帮到那些“至今不好意思问别人,但又拿不准自己是否已经理解了”的人。第一个应该了解的要数“晶体管”了。“晶体管”在电子制作领域是非常常用的易用器件,尤其是在使用Arduino等微控制器控制LED和电机时,晶体管是不可或缺的重要器件。但是,对于电子制作初学者来说,掌握晶体管的使用方法有点难。刚开始电子制作时使用的元器件,比如电池、LED、电阻器和开关等,几乎都是两个引脚,而晶体管却有三个引

关键字:

ROHM 晶体管

本文将解析使 3D NAND、高级 DRAM 和 5nm SoC 成为可能的架构、工具和材料。要提高高级 SoC 和封装(用于移动应用程序、数据中心和人工智能)的性能,就需要对架构、材料和核心制造流程进行复杂且代价高昂的更改。正在考虑的选项包括新的计算架构、不同的材料,包括更薄的势垒层和热预算更高的材料,以及更高纵横比的蚀刻和更快的外延层生长。挑战在于如何以不偏离功率、性能和面积/成本 (PPAC) 曲线太远的方式组合这些。当今的顶级智能手机使用集成多种低功耗、高性能功能的移动 SoC 平台,包括一个或多

关键字:

3D NAND DRAM 5nm SoC

3d 晶体管介绍

您好,目前还没有人创建词条3d 晶体管!

欢迎您创建该词条,阐述对3d 晶体管的理解,并与今后在此搜索3d 晶体管的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473