DRAM迎来3D时代?

3D DRAM 是一种具有新结构的存储芯片,打破了当前陈旧的范式。现有的 DRAM 产品开发侧重于通过减小电路线宽来提高集成度,但随着线宽进入 10 纳米范围,电容器电流泄漏和干扰等物理限制显著增加。为了防止这种情况,引入了高介电常数(高 K)沉积材料和极紫外(EUV)设备等新材料和设备。但半导体行业认为,微型化制造 10 纳米或更先进的芯片将对芯片制造商造成巨大挑战。

本文引用地址:https://www.eepw.com.cn/article/202305/446416.htm一家加利福尼亚公司 NEO 推出了一种解决方案,可以用于通过 3D 堆叠技术提高 DRAM 芯片密度。据称新的存储芯片将大大提高 DRAM 容量,同时仍需要低成本、低维护的制造工作。NEO 表示,3D X-DRAM 是世界上第一个用于 DRAM 内存的类 3D NAND 技术,该解决方案旨在解决 DRAM 的容量瓶颈,同时取代「整个 2D DRAM 市场」。该公司表示其解决方案优于竞争产品,因为它比当今市场上的其他选择更方便。

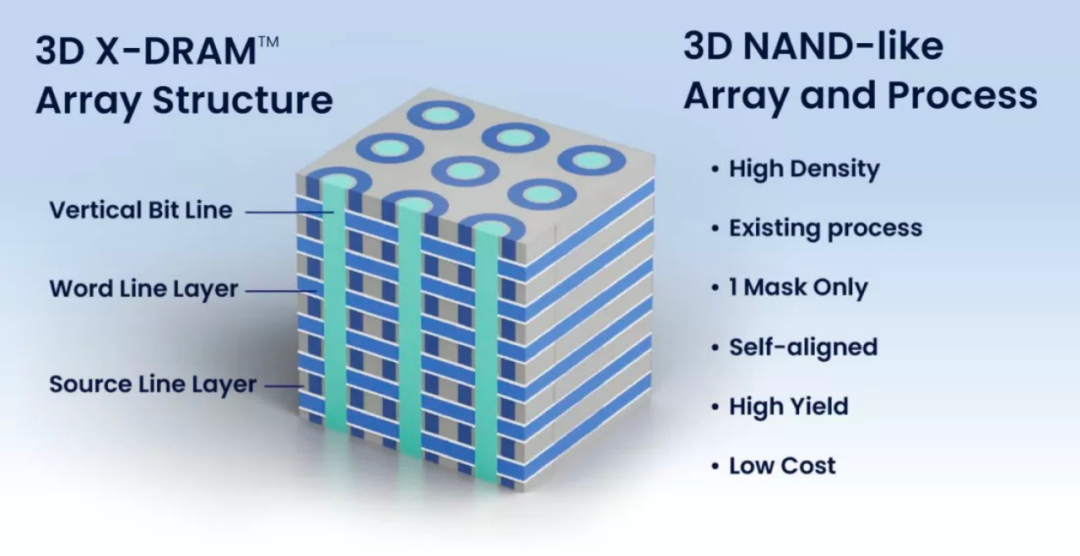

NEO 解释说,3D X-DRAM 采用基于无电容器浮体单元技术的类 3D NAND DRAM 单元阵列结构。3D X-DRAM 芯片可以用目前用于 3D NAND 芯片的相同方法制造,因为它们只需要一个掩模来定义位线孔并在孔内形成单元结构。

这种单元结构简化了工艺步骤,为 3D 系统内存制造提供了「高速、高密度、低成本、高良率的解决方案」。NEO 估计其新的 3D X-DRAM 技术可以实现 128 Gb 的密度和 230 层,比现在的 DRAM 密度高 8 倍。

NEO 表示,全行业正在努力将 3D 堆叠解决方案引入 DRAM 市场。借助 3D X-DRAM,芯片制造商可以利用当前「成熟」的 3D NAND 工艺,而无需存储行业内的学术论文和研究人员提出的更奇特的工艺。

NEO 创始人兼首席执行官、拥有 120 多项美国专利的 Andy Hsu 表示,3D X-DRAM 显然是新兴 3D DRAM 市场中的领先解决方案。这是一种非常简单且成本低廉的制造和扩展解决方案,它可能会蓬勃发展,尤其是在对高密度 DIMM 模块有着迫切需求的服务器市场。

NEO 表示,有关 3D X-DRAM 的相关专利申请已于 2023 年 4 月 6 日随美国专利申请公布一起公布。该公司预计该技术将进一步发展和改进,在 2030 年代中期密度从 128Gb 线性增加到 1Tb。

大厂 3D DRAM 的动作

存储巨头在 3D DRAM 产品研发方面仍处于早期阶段。

美光自 2019 年就已经开始了 3D DRAM 的研究,三星电子和 SK 海力士也在加速 3D DRAM 的商业化。

2021 年,韩国半导体厂商正式开始谈 3D DRAM 的开发。恰逢三星电子于 2021 年在其 DS 部门内建立了下一代工艺开发团队开始研究。

「3D DRAM 被认为是半导体行业未来的增长动力,」三星电子半导体研究中心副总裁兼工艺开发办公室负责人 Lee Jong-myung 在 3 月 10 日于首尔 COEX 举行的 IEEE EDTM 2023 上表示负责 SK 海力士未来技术研究所的 SK 海力士副总裁 Cha Seon-yong 也在 3 月 8 日表示,「到明年左右,有关 3D DRAM 电气特性的细节将被披露,确定他们的发展方向。」

三星电子和 SK 海力士今年量产的尖端 DRAM 线宽为 12 纳米。考虑到目前 DRAM 线宽微缩一纳米的现状,新结构 DRAM 的商品化将成为一种必然,而不是一种选择,三四年后。

三星电子和 SK 海力士可能会加速 3D DRAM 技术的商业化。

与现有的 DRAM 市场不同,3D DRAM 市场并没有绝对的领导者,因此快速量产技术开发至关重要。还需要及时应对由于 ChatGPT 等人工智能的激活而导致的对高性能和大容量存储器半导体的需求增加。

3D DRAM 领域的技术竞争也在升温。据半导体技术分析公司 TechInsights 称,在内存半导体市场排名第三的美光正积极准备蓝海市场,到 2022 年 8 月获得 30 多项 3D DRAM 专利技术。相比不到 15 项 DRAM 三星电子持有的专利和 SK 海力士持有的大约 10 项专利,美光获得的 3D DRAM 相关专利是这两家韩国芯片制造商的两到三倍。三星电子和 SK 海力士分列全球 DRAM 市场第一和第二位。

3D DRAM 可能是革命性的

2013 年闪迪推出的 3D NAND 曾为 NAND 产业带来了革命性的改变,10 年过去,176 层的 3D NAND 已经开始生产,230 层产品即将推出,300 层的产品正在开发。然而,DRAM 在平面时代停滞不前。

三星今年发表了一篇名为「通过第三维进行 DRAM 缩放的持续演进——垂直堆叠 DRAM」的论文,论文中指出:「在过去的几十年里,通过缩小每单位面积的存取晶体管和电容器,DRAM 的密度得到了显著提高。然而,远远超出 10 nm 工艺节点的缩小设备越来越多地带来工艺和可靠性挑战。随着闪存技术通过 3D NAND 取得了关键性的成功创新,DRAM 技术也可能采用垂直堆叠存储单元。垂直堆叠 DRAM (VS-DRAM) 通过增加层数以及减小晶体管的尺寸来继续提高芯片上的位密度。」

评论