3D芯片技术是Meta AR原型芯片获得巨大性能提升的关键

META

增强现实(AR)系统的设计存在许多限制因素。近日,Meta公司的研究科学家Tony Wu在IEEE国际固态电路会议(ISSCC,https://www.isscc.org/)上对工程师们介绍了其AR原型芯片,他提到最重要的是“当你四处走动时,你必须看起来舒适”。

AR(https://spectrum.ieee.org/tag/augmented-reality)系统也必须是轻量级的,不能释放大量热量。它需要节省电力 —— 因为没有人想每隔几个小时就给可穿戴电子设备充电一次。Wu是Meta团队的一员,该团队致力于开发硅智能,以制造一种名为Aria的AR系统(https://www.projectaria.com/)。Wu告诉工程师,解决方案的很大一部分是3D芯片集成技术(https://spectrum.ieee.org/amd-3d-stacking-intel-graphcore)。在ISSCC上,Meta详细介绍了其AR原型芯片是如何使用3D技术在相同的区域以相同或更少的能量做更多的事情。

META

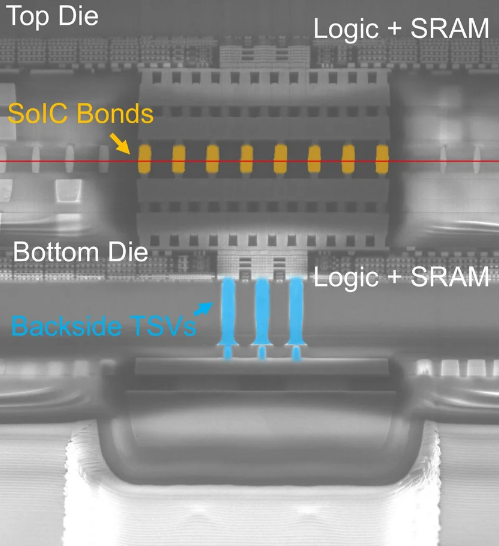

原型芯片是两个尺寸相等的集成电路组成,尺寸为4.1x3.7毫米。它们在一种称为面对面晶圆到晶圆(face-to-face wafer-to-wafer)混合键合(hybrid bonding)的过程中键合在一起。顾名思义,它包括翻转两个完全处理过的晶片,使它们彼此面面对并粘合,以便它们的直接连接在一起。混合键合意味着它是铜对铜的直接连接,无需焊接。

采用台积电(TSMC,https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/SoIC.htm - SoIC_WoW)技术意味着两块硅可以大约每2微米形成一次垂直连接。原型并没有完全利用这种密度:它需要两片硅之间大约3.3万个信号连接和600万个电源连接。底部芯片使用硅通孔(TSV)——向下穿过硅的垂直连接——将信号从芯片中输入并通电。

3D堆叠意味着该团队可以在不增加芯片尺寸的情况下提高芯片的计算能力,使其能够处理更大的任务。该芯片的机器学习单元在底部芯片上有四个计算核心和1兆字节的本地内存,但顶部芯片又增加了3兆字节,可以通过27000个垂直数据通道以相同的速度和能量访问——0.15pJ/Byte——就好像它们是一大块硅一样。

该团队在机器学习任务上测试了该芯片,该任务对增强现实、手部跟踪至关重要。该3D芯片能够同时跟踪两只手,所用的能量比单个芯片仅用一只手所能消耗的能量低40%。更重要的是,它的速度提高了40%。

除了机器学习,该芯片还能完成图像处理任务,3D在这里再次发挥了很大的作用。2D版本仅限于压缩图像,而3D芯片可以使用相同数量的能量实现全高清。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。