基于EPM7064的多串口管理系统设计

1 概述

本文引用地址:https://www.eepw.com.cn/article/20971.htm串行接口在数据通信中一直扮演着重要角色。他不仅没有因为时代的进步被淘汰,反而在性能上越来向其极限挑战。usb接口是当前pc机上的主流接口,但仍然有许多外设使用串口与pc机通信,尤其是在工业控制领域。普通pc机所提供的串口资源往往是不够的。

传统扩展多个串行口的方法是利用多个中断源,每个中断通常被分配给单一的设备。这是因为当多于1个的设备被设置成使用同一个特定中断时,系统不能辨认哪个设备使用中断线,所以就会产生混乱。但在嵌入式系统中,花费大量的中断源来扩展串口无疑是资源的浪费。针对这种情况,为了节省紧张的系统资源,本方案通过对cpld的设计,采用1个中断源高效管理多个串口的有效方法实现了将pc主机上的一个usb接口扩展为8个通用串口接口,同时保证了多个串口中断的无漏监测与服务。

2 系统硬件设计

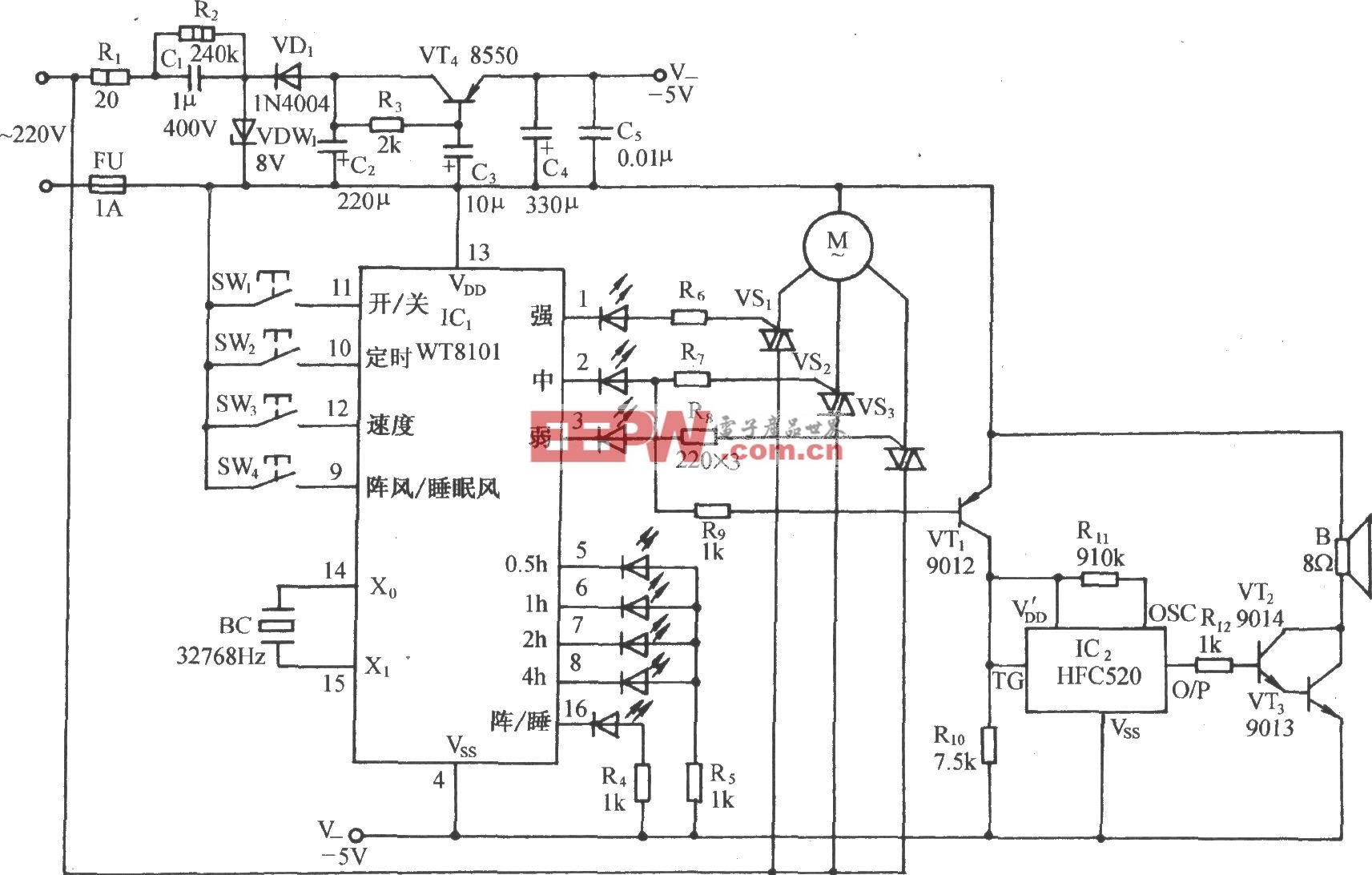

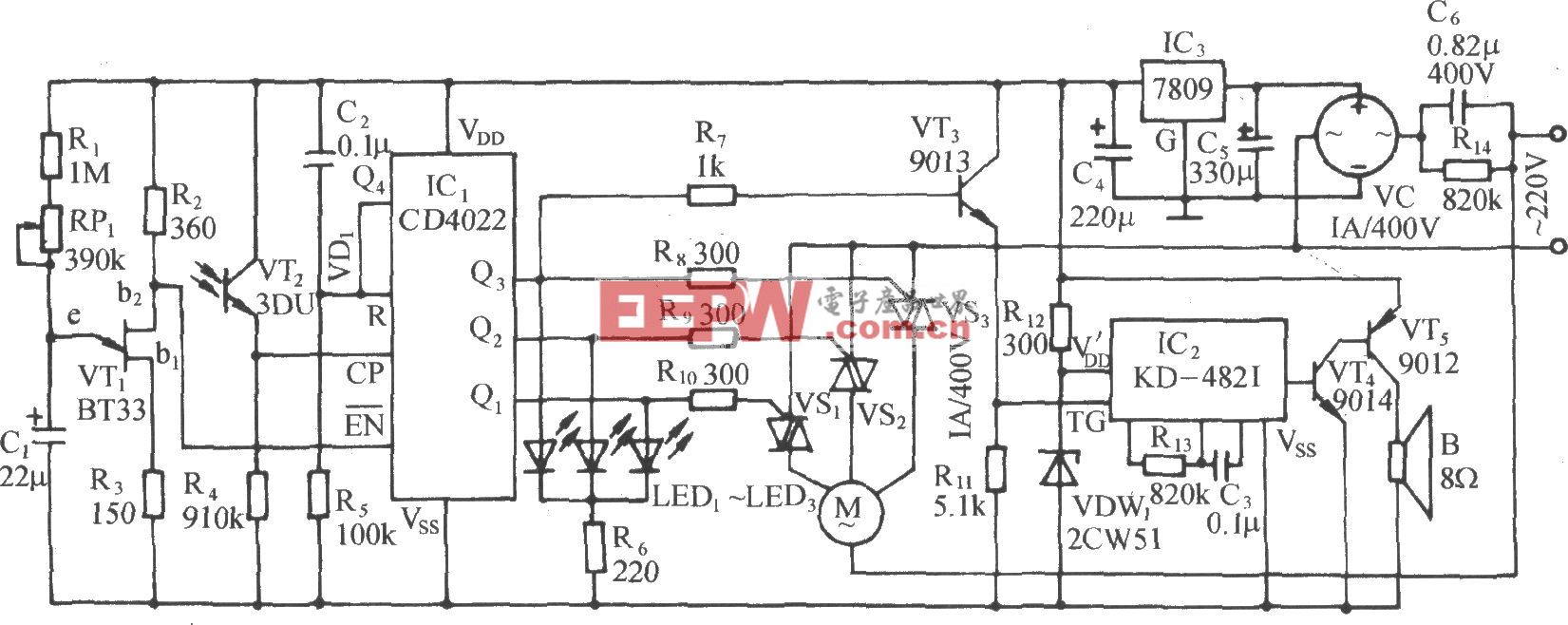

本设计方案(参见图1)采用atmel公司的89c52单片机来控制串口到usb接口之间的数据收发工作,选用philips公司的usb接口芯片pdiusbd12实现单片机与usb器件之间的连接,多串口扩展以tl16c554芯片实现,并由一片cpld(altera的epm7064)实现高效多串口中断源管理,利用单一的中断源来管理多个扩展串口。在pc主机端,设计开发了wdm设备驱动程序对usb口进行虚拟管理,从而使得windows应用程序能以访问普通串口的方式访问串口服务器上的多个串口。

3 cpld设计

本设计中用cpld设计了译码电路、锁存电路、逻辑或电路、三态门电路、状态机电路。由于对宏单元和管脚的要求不是很多,因此选用altera epm7064,44脚,plcc封装。

3.1 译码电路

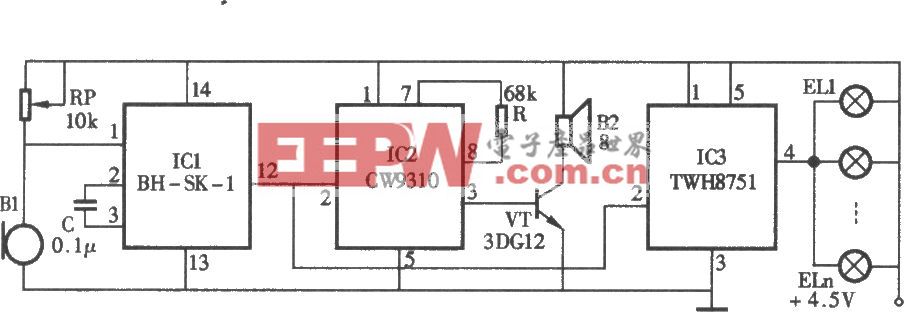

用cpld进行pdiusbd12的选址,2片tl16c554共8个口的选址,以及对cpld中一位寄存器的选址,共用到a3~a7以及do进行译码,译码设计图如图2所示。

(1) pdiusbd12的选址

由于po口为数据地址线,所以要经过地址锁存器,以及a7,a6一起连到一个138译码器上。因为pdiusbd12奇地址表示命令,偶地址表示数据,所以把2个地址接异或非门后再接到pdiusbd12的片选端。如图2上的cs2,其地址为0x7000,0x7001。

(2) tl16c554的选址

为了选中扩展的8个串口,将a3~a5连入另一个138译码器,将其译码为8个选通端连到每个芯片的片选上,然后用a6,a7,do的译码cs0(见图2)作为第二个138译码器的低使能端。其8个口的地址依次为0x0c000,0x0c800,0x0d000,0x0d800,0x0e000,0x0e800,0x0f000,0x0f800。

(3) 一位寄存器的选址

cpld内的一位寄存器的地址设定为0x0c001。

3.2 多串口中断源解决方案

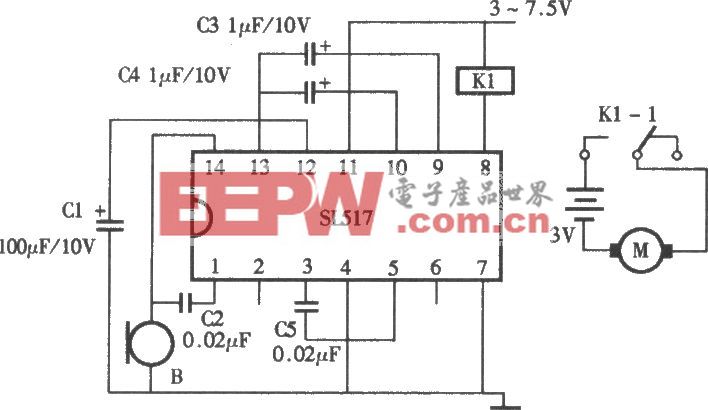

其基本原理如图3所示。

rs232串口通过驱动芯片max202或max232转化成ttl电平,通过串口异步通信器件16c554输出中断请求,通过或门获得多个串口的中断请求,再通过cpld与中断控制器相连接。中断控制线intreq通过cpld主要是在cpld中做一个一位寄存器inten(如图4所示),用作中断允许位,并根据16c554的中断请求intreq和inten的状态来最终生成中断dly_irq,cpu将实时响应该中断请求。

在中断服务过程中,cpu按顺序逐个检查多个扩展口的串口中断源,有中断请求的就给予服务。当刚刚检测过的中断又出现时,一方面靠cpld中的移位寄存器intreq锁存,另一方面,当上一中断服务完成时,cpld中的8位状态机(如图7)保证了一定的延时。此延时中,中断控制程序把堆栈中的内容返回给cpu的寄存器,恢复能获得的响应。这样,即使在多个串口中断密集发生的环境下,扩展的多个串口仍可获得实时性和可靠性较高的中断。具体做法如下:

在中断服务过程中,cpu按顺序逐个检查多个扩展口的串口中断源,有中断请求的就给予服务。当刚刚检测过的中断又出现时,一方面靠cpld中的移位寄存器intreq锁存,另一方面,当上一中断服务完成时,cpld中的8位状态机(如图7)保证了一定的延时。此延时中,中断控制程序把堆栈中的内容返回给cpu的寄存器,恢复能获得的响应。这样,即使在多个串口中断密集发生的环境下,扩展的多个串口仍可获得实时性和可靠性较高的中断。具体做法如下:

(1) intreq为n个中断的或结果。

(2) cpu对inten只写,操作过程分3步:

①中断安装后设置inten=1;

②进入中断服务程序后cpu设置inten=0;

③退出中断服务程序的最后指令再将inten=1。

(3)中断响应的时序图,如图5所示。

在isr置位期间,有中断请求intreq产生时,此时如果触发了中断,则会使上次中断服务无法完成,因而造成中断丢失。因此,在isr配置期间,将中断允许inten设置为o,防止其他中断请求触发中断,并用intreq锁存未被响应的中断请求。退出中断服务后,得中断允许inten设置为1,保证其他中断请求被响应,并延迟50μs,以确保此次中断服务完全退出。

在isr置位期间,有中断请求intreq产生时,此时如果触发了中断,则会使上次中断服务无法完成,因而造成中断丢失。因此,在isr配置期间,将中断允许inten设置为o,防止其他中断请求触发中断,并用intreq锁存未被响应的中断请求。退出中断服务后,得中断允许inten设置为1,保证其他中断请求被响应,并延迟50μs,以确保此次中断服务完全退出。

(4)中断控制寄存器的状态图(描述8位状态机的转换)如图6所示。

3.3 epm7064的接口电路图

3.3 epm7064的接口电路图

本设计支持epm7064在线下载功能,其接口图如图8所示。

4 虚拟串口驱动程序设计

4 虚拟串口驱动程序设计

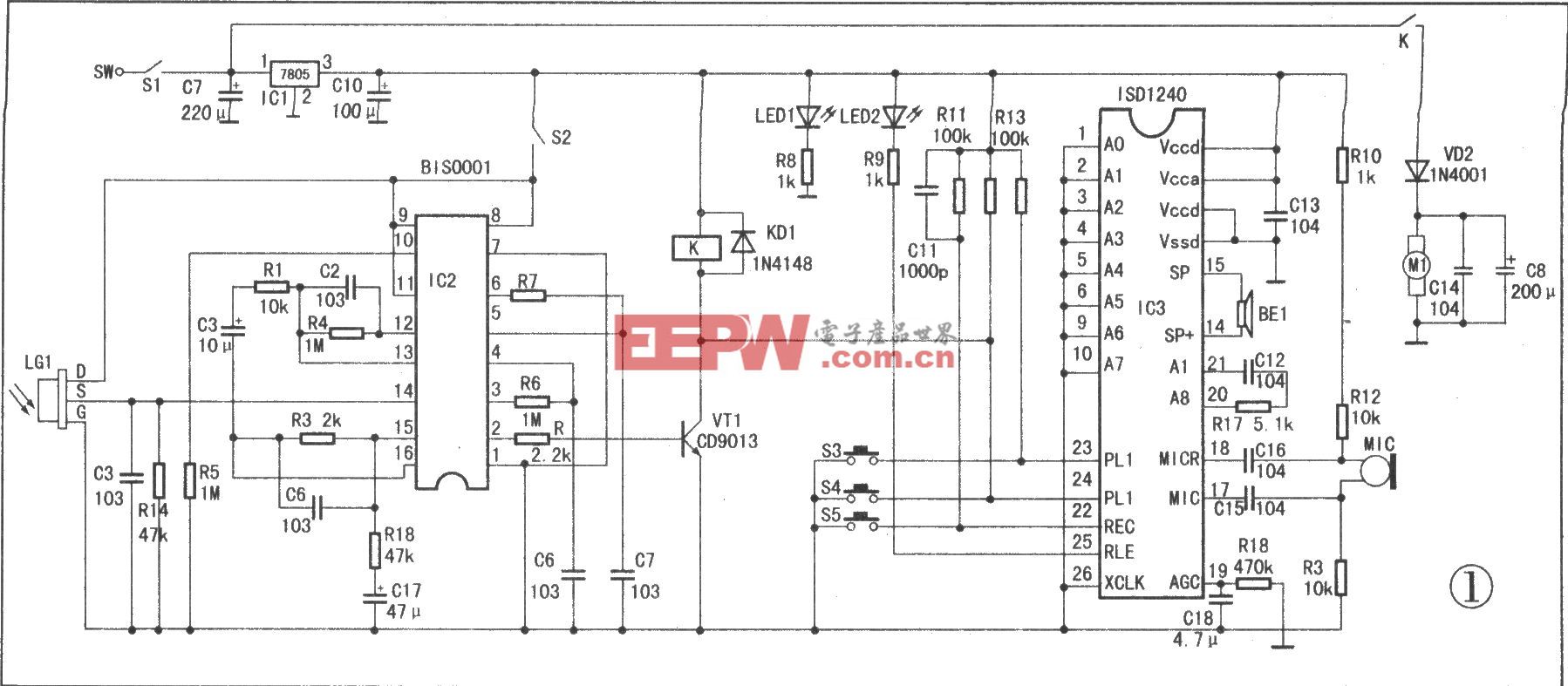

为实现主机可以如操作本机串口一样通过主机usb口对串口设备进行数据读取,主机端设备驱动程序需将串口服务器的8个串口对应到主机的8个虚拟串口上。在wdm设备驱动程序设计中,这样的功能可以通过在usb功能驱动程序上层加上一个过滤驱动层来实现。应用程序发送数据到虚拟串口,而过滤驱动程序则将虚拟串口中的数据转发给usb功能驱动程序,反之亦然。基于wdm的usb设备驱动程序分层结构如图9所示。

评论