全面解读集成电路产业链及相关技术

(2)晶圆加工

本文引用地址:https://www.eepw.com.cn/article/201707/361307.htm晶圆加工技术是指在晶圆上制造用于电气电子设备中的集成电路的过程。该技术是一个多步骤、反复处理的过程。在实施过程中多次重复运用掺杂、沉积、光刻等工艺,最终实现将高集成度的复杂电路“印制”在半导体基质上的目的。整个晶圆加工过程一般历时六至八周,需要在高度专业化的晶圆加工厂中进行。

无尘车间

1)操作类型

晶圆加工过程与晶圆制造不同,晶圆加工领域的工厂各自遵循本公司特有的生产流程。同时,先进的加工技术逐年推陈出新,使得生产流程不断地发生着改变。但是多样化的制程工艺无外乎从属于以下四个范畴:沉积、清除、成像、电学性质改变。

沉积是指制程中涉及生长、涂覆或将其他材料转移至晶圆上的步骤。沉积技术包括物理气相沉积(PVD)、化学气相沉积(CVD)、电化学沉积(ECD)、分子束外延(MBE)、相对先进的原子层沉积(ALD)以及其他技术。

清除是指从晶圆上清除材料的技术。例如蚀刻工艺(湿蚀刻或干蚀刻)与化学机械研磨技术(CMP)。

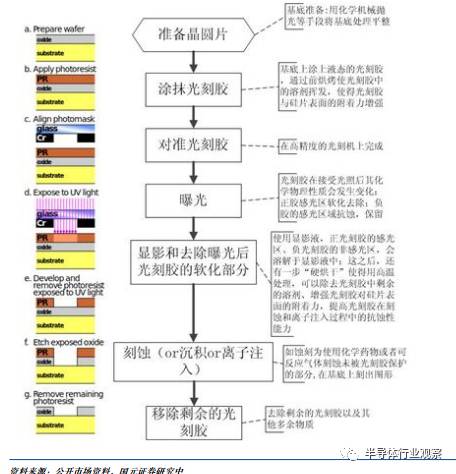

成像塑造或改变沉积的材料,一般称为光刻技术。例如,常见的光刻工艺先将晶圆表面覆盖一层化学物质——光刻胶,之后光刻机聚焦、校准并移动印有电路图的光罩,将晶圆上的选中部分曝光于短波光线下。被曝光的区域此后被显影剂溶液洗去。在蚀刻或其他制程之后,剩余的光刻胶由等离子体灰化法清除。

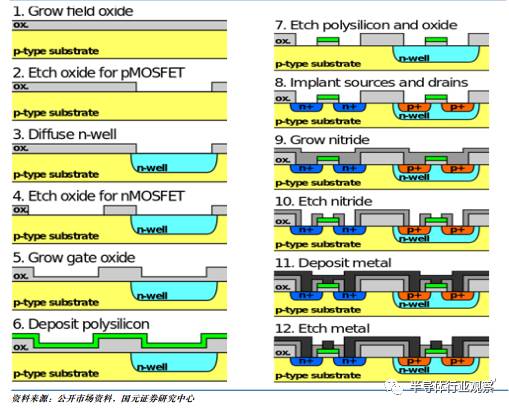

电学性质改变指掺杂半导体,形成源极与漏极的步骤。该技术过去由扩散炉技术实现,现在多运用离子植入技术。掺杂过程之后晶圆接受炉内退火或更先进的快速热退火(RTA)处理。退火过程激活了植入的掺杂剂。电学性质改变目前也包括了通过紫外线制程降低low-k绝缘体材料介电常数的技术。

高端集成电路设计复杂,所需制程步骤繁多;多层金属连接层技术用以实现大量元件间的有效连接。当代芯片加工多经历300多道制程步骤;可包含11层的金属导线层。

光刻原理

掺杂及构建CMOS单元原理

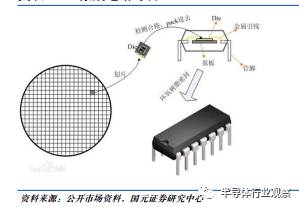

加工好的晶圆在晶圆测试后,将进入芯片封装厂商,进行最后的封装测试。

2)制程逻辑

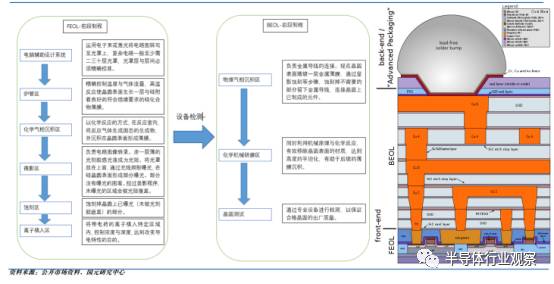

“印刻”于晶圆上的半导体元件需以金属导体连接以实现特定的电路功能。以上各种技术工艺按制程的先后顺序,可划分为前段制程(FEOL)与后段制程(BEOL)。以集成于芯片上的元件的相互连接为分水岭:FEOL指沉积金属导电层以前,于半导体基质上形成独立元件(如三极管、电容、电阻、独立的CMOS)的前半段制程;BEOL指金属层沉积后,创建金属导线,连接元件,并构成绝缘各导线的介电层的后半段制程。

晶圆加工制程图例

左图体现晶圆加工前段制程与后段制程的具体内容;右图为晶圆上单个CMOS模块的纵切图,从下到上的三个部分符合芯片的三个制程:FEOL前段制程、BEOL后段制程、Packaging封装制程。

(三)封装部分

集成电路封装是半导体设备制造过程中的最后一个环节。在该环节中,微小的半导体材料模块会被臵于一个保护壳内,以防止物理损坏或化学腐蚀。集成电路芯片将通过封装“外壳”与外部电路板相连。

封装过程后,通过封装测试的成品集成电路设备,将作为成品最终投入的下游设备的应用中去。

集成电路的封装

(1)封装技术的发展演变

追随摩尔定律,芯片集成度日益提高,单体集成电路需要日益增多的引脚与外部设备连接,以实现更复杂的逻辑控制功能;同时,随着科技进步,各类电子设备向着小型化、智能化发展,电路系统的微缩要求集成电路芯片的体量不断减小。所以,保证性能的前提下,“多引脚、小体量”的芯片封装始终是集成电路封装技术的发展方向。随着封装技术的发展,集成电路封装模式不断推陈出新。目前,各种封装技术均用于不同的市场领域。这里,按照各种工艺出现的先后顺序介绍市场上主流的一些封装技术。

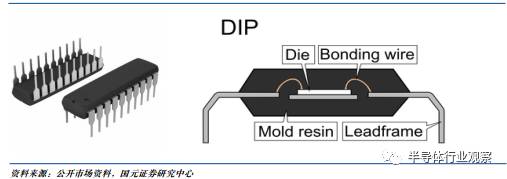

最早的集成电路封装于扁平的陶瓷管体内,由于其可靠性与较小的体量,在军事领域被应用多年。随后陶瓷管体的封装模式很快进步至塑料管体的 DIP(双列直插式封装)。

双列直插式封装

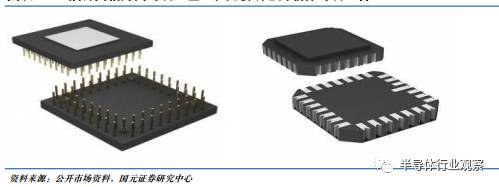

在1980年代,VLSI规模集成电路的引脚数量超过了DIP封装的技术限制。PGA(插针网格阵列)封装及LCC(无引线芯片载体)封装投入生产,用以突破DIP封装的限制。

插针网格阵列封装(左)和无引线芯片载体封装(右)

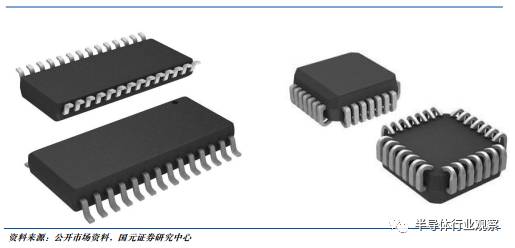

表面黏着式封装出现于80年代早期,并于80年代末期兴盛。用于小外形集成电路的鸥翼型封装与J-引脚封装采用优化的引脚间距,使得运用该技术的封装比等效的DIP封装占用面积少30-50%,厚度薄70%。

鸥翼型封装(左)和 J-引脚封装(右)

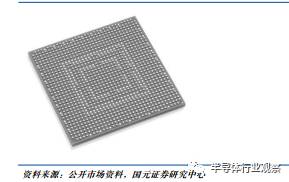

下阶段,封装技术迎来了巨大的技术创新——表面阵列封装。该技术在封装管体的表面铺设连接节点,因此得以提供比此前封装技术更多的外部连接(此前的封装方式只在管体周围引出接点)。其中 BGA(球栅阵列)封装成为广泛应用的封装技术之一。

球栅阵列封装

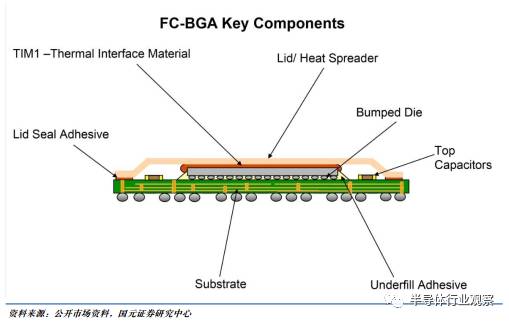

BGA封装技术在1970年代便已经存在。1990年代,该技术演进至FCBGA(倒装芯片球栅阵列)封装。FCBGA封装允许存在多于任何封装技术的针脚数量。在FCBGA管壳内,晶片被正面朝下倒装并通过类似于印刷电路板的基体(不通过引线),与管体球栅建立连接。因此FCBGA可以允许成阵列的输入输出信号分散连接至整个晶片表面,而非限制于芯片四周。

倒装芯片球栅阵列封装

评论