浅谈使用可定制微控制器高效开发系统级芯片 (SoC)

为了应对成本、尺寸、功耗和开发时间的压力,许多电子产品都建构于系统级芯片 (SoC)之上。这个单片集成电路集成了大多数的系统功能。然而,随着这些器件越来越复杂,要在有限的时间里经济地进行产品开发以满足产品上市时间的压力已变得越来越困难。SoC集成了一些可编程部件 (特别是微控制器),使得其软件开发与硬件开发同样的昂贵和耗时。

本文引用地址:https://www.eepw.com.cn/article/161899.htm使用基于业界标准、带有片上存储器和各种标准接口的ARMò处理器,再加上面向特定应用逻辑和非标接口的金属可编程模块 (MP模块),构成的可定制微控制器是切实可行的SoC开发方法,能够解决上述问题:

-采用预先已经准备好的基础晶圆,仅针对定制部分添加金属层,可以缩短器件生产制造的时间。

-最大限度地减少集成特定应用逻辑方面的设计耗费,并减少制备工艺中所需的光罩数,可以降低开发成本。

-仿真板包括了处理器、内存、外设和标准接口,并用FPGA来代替MP模块,实现了软/硬件全速并行测试,提高了器件生产制造和软件开发的首次成功率。

新一代的ARM9处理器,通过全新的设计,采用了更多的晶体管,能够达到两倍以上于ARM7处理器的处理能力。这种处理能力的提高是通过增加时钟频率和减少指令执行周期实现的。

(一) 时钟频率的提高:ARM7处理器采用3级流水线,而ARM9采用5级流水线。增加的流水线设计提高了时钟频率和并行处理能力。5级流水线能够将每一个指令处理分配到5个时钟周期内,在每一个时钟周期内同时有5个指令在执行。在同样的加工工艺下,ARM9TDMI处理器的时钟频率是ARM7TDMI的1.8~2.2倍。

(二) 指令周期的改进:指令周期的改进对于处理器性能的提高有很大的帮助。性能提高的幅度依赖于代码执行时指令的重叠,这实际上是程序本身的问题。

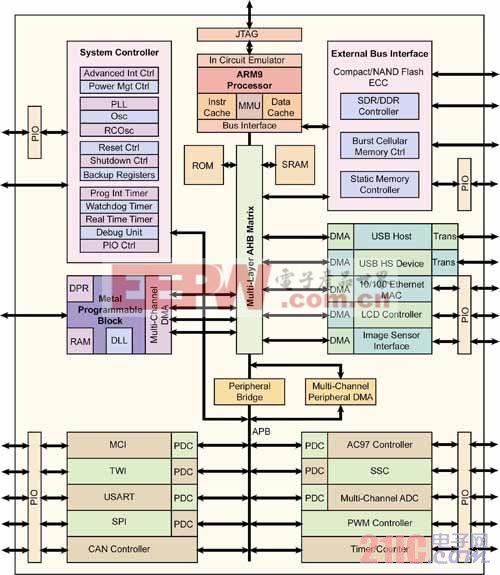

图1:基于ARM9的可定制微控制器架构

如图1所示,可定制微控制器的基础为业界标准的ARM7或ARM9处理器内核,以及连接片上SRAM和ROM、外部总线接口和系统外设的多层AHB总线矩阵,并可桥接面向系统控制器和低速外设的高能效APB。该架构的一个主要特点是分布式DMA,这种DMA加上由AHB总线矩阵提供的并行数据通道,能为器件提供极高的内部数据带宽。器件中的MP模块具有多个DMA端口,因此由其实现的专用IP也能受益于这种高速内部带宽。

评论